தி புலம்-விளைவு டிரான்சிஸ்டர் (FET) என்பது ஒரு மின்னணு சாதனம், இதில் ஒரு மின்சார புலம் மின்னோட்டத்தின் ஓட்டத்தை கட்டுப்படுத்த பயன்படுகிறது. இதைச் செயல்படுத்த, சாதனத்தின் வாயில் மற்றும் மூல முனையங்கள் முழுவதும் சாத்தியமான வேறுபாடு பயன்படுத்தப்படுகிறது, இது வடிகால் மற்றும் மூல முனையங்களுக்கிடையேயான கடத்துத்திறனை மாற்றுகிறது, இதனால் இந்த முனையங்களில் கட்டுப்படுத்தப்பட்ட மின்னோட்டம் பாய்கிறது.

FET கள் என்று அழைக்கப்படுகின்றன unipolar டிரான்சிஸ்டர்கள் ஏனெனில் இவை ஒற்றை-கேரியர் வகை சாதனங்களாக செயல்பட வடிவமைக்கப்பட்டுள்ளன. பல்வேறு வகையான புல விளைவு டிரான்சிஸ்டர்கள் கிடைக்கும்.

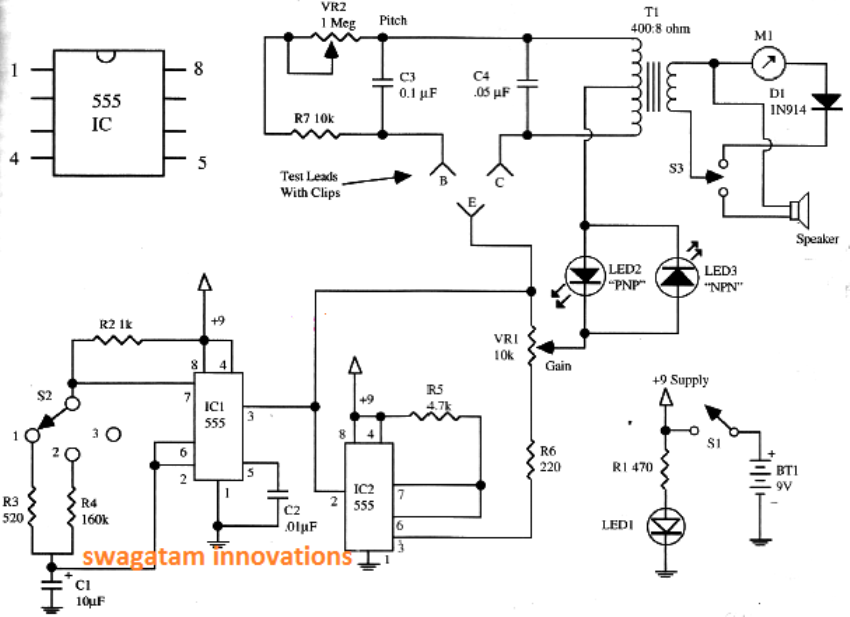

சின்னம்

N- சேனல் மற்றும் பி-சேனல் JFET களுக்கான வரைகலை சின்னங்களை பின்வரும் புள்ளிவிவரங்களில் காட்சிப்படுத்தலாம்.

நான் எந்த திசையை குறிக்க என்-சேனல் சாதனத்திற்கு உள்நோக்கி சுட்டிக்காட்டும் அம்பு குறிகள் என்பதை நீங்கள் தெளிவாக கவனிக்க முடியும்ஜி(கேட் கரண்ட்) பி-என் சந்தி முன்னோக்கி-சார்புடையதாக இருக்கும்போது பாயும்.

பி-சேனல் சாதனத்தின் விஷயத்தில் அம்பு சின்னத்தின் திசையில் உள்ள வேறுபாட்டைத் தவிர நிலைமைகள் ஒரே மாதிரியாக இருக்கும்.

FET க்கும் BJT க்கும் இடையிலான வேறுபாடு

புலம்-விளைவு டிரான்சிஸ்டர் (FET) என்பது மூன்று முனைய சாதனமாகும், இது பிஜேடி டிரான்சிஸ்டரின் சாதனங்களை ஒரு பெரிய அளவிற்கு பூர்த்தி செய்யும் பரந்த அளவிலான சுற்று பயன்பாடுகளுக்காக வடிவமைக்கப்பட்டுள்ளது.

BJT களுக்கும் JFET களுக்கும் இடையில் குறிப்பிடத்தக்க மாறுபாடுகளை நீங்கள் காணலாம், உண்மையில் பல பொருந்தக்கூடிய பண்புகள் உள்ளன, அவை பின்வரும் விவாதங்களில் பேசப்படும். இந்த சாதனங்களுக்கிடையேயான முக்கிய வேறுபாடு படம் 5.1 அ இல் குறிப்பிடப்பட்டுள்ளபடி தற்போதைய கட்டுப்படுத்தப்பட்ட சாதனமாகும், அதே நேரத்தில் JFET டிரான்சிஸ்டர் படம் 5.1 பி இல் சுட்டிக்காட்டப்பட்டுள்ளபடி மின்னழுத்தத்தால் கட்டுப்படுத்தப்பட்ட சாதனமாகும்.

எளிமையாகச் சொன்னால், தற்போதைய நான்சிபடம் 5.1a என்பது I இன் மட்டத்தின் உடனடி செயல்பாடுபி. FET க்கு தற்போதைய நான் மின்னழுத்த V இன் செயல்பாடுஜி.எஸ்படம் 5.1 பி இல் காட்டப்பட்டுள்ளபடி உள்ளீட்டு சுற்றுக்கு வழங்கப்படுகிறது.

இரண்டு நிகழ்வுகளிலும் வெளியீட்டு சுற்று மின்னோட்டம் உள்ளீட்டு சுற்றுகளின் அளவுருவால் நிர்வகிக்கப்படும். ஒரு சூழ்நிலையில் தற்போதைய நிலை மற்றும் மற்றொன்று பயன்படுத்தப்பட்ட மின்னழுத்தம்.

இருமுனை டிரான்சிஸ்டர்களுக்கான npn மற்றும் pnp ஐப் போலவே, நீங்கள் n- சேனல் மற்றும் p- சேனல் புலம்-விளைவு டிரான்சிஸ்டர்களைக் காண்பீர்கள். ஆனால், பிஜேடி டிரான்சிஸ்டர் ஒரு இருமுனை சாதனம் என்பதை நீங்கள் நினைவில் கொள்ள வேண்டும், இது முன்னொட்டு இரு- கடத்தல் நிலை என்பது இரண்டு சார்ஜ் கேரியர்கள், எலக்ட்ரான்கள் மற்றும் துளைகளின் செயல்பாடு என்பதைக் குறிக்கிறது.

மறுபுறம் FET ஒரு unipolar சாதனம் இது எலக்ட்ரான் (என்-சேனல்) அல்லது துளை (பி-சேனல்) கடத்துதலைப் பொறுத்தது.

'புலம்-விளைவு' என்ற சொற்றொடரை இவ்வாறு விளக்கலாம்: எந்தவொரு உடல் தொடர்பும் இல்லாமல் காந்தத்தை நோக்கி உலோகத் தாக்கங்களை ஈர்க்க நிரந்தர காந்தத்தின் ஆற்றலை நாம் அனைவரும் அறிவோம். FET க்குள் இதேபோன்ற வழியில் ஒரு மின் புலம் தற்போதுள்ள கட்டணங்களால் உருவாக்கப்படுகிறது, இது கட்டுப்பாட்டு மற்றும் கட்டுப்படுத்தப்பட்ட அளவுகளுக்கு இடையே நேரடி தொடர்பு இல்லாமல் வெளியீட்டு சுற்றுகளின் கடத்தல் பாதையை பாதிக்கிறது. FET இன் மிக முக்கியமான அம்சங்களில் ஒன்று அதன் உயர் உள்ளீட்டு மின்மறுப்பு ஆகும்.

1 முதல் பல நூறு மெகாஹாம் வரையிலான வரம்பில் இது பிஜேடி உள்ளமைவுகளின் இயல்பான உள்ளீட்டு எதிர்ப்பு வரம்புகளை கணிசமாக விஞ்சி நிற்கிறது, இது நேரியல் ஏசி பெருக்கி மாதிரிகளை உருவாக்கும் போது மிக முக்கியமான பண்பு.

இருப்பினும், உள்ளீட்டு சமிக்ஞையின் மாறுபாடுகளுக்கு பிஜேடி அதிக உணர்திறனைக் கொண்டுள்ளது. பொருள், வெளியீட்டு மின்னோட்டத்தின் மாற்றம் பொதுவாக பி.ஜே.டி-க்களை விட FET களை விட கணிசமாக அதிகமாக உள்ளது, அவற்றின் உள்ளீட்டு மின்னழுத்தங்களில் அதே அளவு மாற்றம்.

இதன் காரணமாக, பி.ஜே.டி பெருக்கிகளுக்கான நிலையான ஏசி மின்னழுத்த ஆதாயங்கள் FET களுடன் ஒப்பிடும்போது மிக அதிகமாக இருக்கும்.

பொதுவாக, FET கள் BJT களை விட கணிசமாக வெப்ப நெகிழக்கூடியவை, மேலும் BJT களுடன் ஒப்பிடும்போது அவை பெரும்பாலும் சிறிய அளவிலான கட்டமைப்பில் உள்ளன, அவை ஒருங்கிணைந்த-சுற்று (Iசி)சீவல்கள்.

சில FET களின் கட்டமைப்பு பண்புகள், மறுபுறம், அவை BJT களை விட உடல் தொடர்புகளுக்கு கூடுதல் உணர்திறன் கொண்டதாக இருக்க அனுமதிக்கும்.

மேலும் BJT / JFET உறவு

- ஒரு பிஜேடி விஇரு= 0.7 V என்பது அதன் உள்ளமைவின் பகுப்பாய்வைத் தொடங்க முக்கியமான காரணியாகும்.

- இதேபோல், அளவுரு I.ஜி= 0 A என்பது பொதுவாக JFET சுற்று பகுப்பாய்வுக்கு கருதப்படும் முதல் விஷயம்.

- பிஜேடி உள்ளமைவுக்கு, நான்பிபெரும்பாலும் தீர்மானிக்க வேண்டிய முதல் காரணியாகும்.

- அதேபோல், JFET ஐப் பொறுத்தவரை, இது பொதுவாக விஜி.எஸ்.

இந்த கட்டுரையில் நாம் JFET கள் அல்லது சந்தி புலம் விளைவு டிரான்சிஸ்டர்கள் மீது கவனம் செலுத்துவோம், அடுத்த கட்டுரையில் மெட்டல்-ஆக்சைடு-செமிகண்டக்டர் புலம்-எஃப்செட் டிரான்சிஸ்டர் அல்லது MOS-FET பற்றி விவாதிப்போம்.

JFET களின் கட்டுமானம் மற்றும் பண்புகள்

நாங்கள் ஆரம்பத்தில் கற்றுக்கொண்டது போல் ஒரு JFET க்கு 3 தடங்கள் உள்ளன. அவற்றில் ஒன்று மற்ற இரண்டிற்கும் இடையிலான தற்போதைய ஓட்டத்தை கட்டுப்படுத்துகிறது.

பி.ஜே.டி.களைப் போலவே, ஜே.எஃப்.இ.டி.களிலும் என்-சேனல் சாதனம் பி-சேனல் சகாக்களை விட முக்கியமாகப் பயன்படுத்தப்படுகிறது, ஏனெனில் பி-சாதனத்துடன் ஒப்பிடும்போது என் சாதனங்கள் மிகவும் திறமையாகவும் பயனர் நட்பாகவும் இருக்கும்.

பின்வரும் படத்தில் ஒரு n- சேனல் JFET இன் அடிப்படை கட்டமைப்பு அல்லது கட்டுமானத்தைக் காணலாம். N- வகை கலவை p- வகை அடுக்குகளில் முதன்மை சேனலை உருவாக்குவதை நாம் காணலாம்.

N- வகை சேனலின் மேல் பகுதி ஓம்மிக் தொடர்பு மூலம் வடிகால் (டி) என்ற பெயரில் இணைக்கப்பட்டுள்ளது, அதே சேனலின் கீழ் பகுதியும் மூல (எஸ்) என்ற மற்றொரு முனையத்துடன் ஓமிக் தொடர்பு மூலம் இணைக்கப்பட்டுள்ளது.

பி-வகை பொருட்கள் ஜோடி கேட் (ஜி) என குறிப்பிடப்படும் முனையத்துடன் இணைக்கப்பட்டுள்ளன. அடிப்படையில் வடிகால் மற்றும் மூல முனையங்கள் n- வகை சேனலின் முனைகளில் இணைக்கப்பட்டுள்ளன. கேட் முனையம் ஒரு ஜோடி பி-சேனல் பொருளுடன் இணைக்கப்பட்டுள்ளது.

ஒரு jfet முழுவதும் மின்னழுத்தம் பயன்படுத்தப்படாதபோது, அதன் இரண்டு p-n சந்திகள் எந்த சார்பு நிலைமைகளும் இல்லாமல் உள்ளன. இந்த சூழ்நிலையில், மேலே உள்ள படத்தில் சுட்டிக்காட்டப்பட்டுள்ளபடி ஒவ்வொரு சந்திப்பிலும் ஒரு குறைப்பு பகுதி உள்ளது, இது ஒரு சார்பு இல்லாமல் ஒரு டையோடு பி-என் பகுதி போல தோன்றுகிறது.

நீர் ஒப்புமை

JFET இன் வேலை மற்றும் கட்டுப்பாட்டு செயல்பாடுகளை பின்வரும் நீர் ஒப்புமை மூலம் புரிந்து கொள்ள முடியும்.

இங்கே, நீர் அழுத்தத்தை வடிகால் முதல் மூலத்தை நோக்கி பயன்படுத்தப்படும் மின்னழுத்த அளவோடு ஒப்பிடலாம்.

நீரின் ஓட்டத்தை எலக்ட்ரான்களின் ஓட்டத்துடன் ஒப்பிடலாம். குழாயின் வாய் JFET இன் மூல முனையத்தைப் பின்பற்றுகிறது, அதே நேரத்தில் குழாய் மேல் பகுதி தண்ணீர் கட்டாயப்படுத்தப்படுவதால் JFET இன் வடிகால் சித்தரிக்கப்படுகிறது.

குழாய் குமிழ் JFET இன் கேட் போல செயல்படுகிறது. ஒரு உள்ளீட்டு ஆற்றலின் உதவியுடன், வாய்க்கால் திறக்கும் போது நீரின் ஓட்டத்தை குழாய் குமிழ் கட்டுப்படுத்துவதைப் போல, வடிகால் முதல் மூலத்திற்கு எலக்ட்ரான்கள் (கட்டணம்) ஓட்டத்தை கட்டுப்படுத்துகிறது.

JFET கட்டமைப்பிலிருந்து, வடிகால் மற்றும் மூல முனையங்கள் n- சேனலின் எதிர் முனைகளில் இருப்பதைக் காணலாம், மேலும் இந்த சொல் எலக்ட்ரான் ஓட்டத்தை அடிப்படையாகக் கொண்டிருப்பதால் நாம் எழுதலாம்:

விஜி.எஸ்= 0 வி, விடி.எஸ்சில நேர்மறை மதிப்பு

படம் 5.4 இல் நாம் ஒரு நேர்மறை மின்னழுத்தம் V ஐக் காணலாம்டி.எஸ்n- சேனல் முழுவதும் பயன்படுத்தப்பட்டது. வி நிபந்தனை உருவாக்க கேட் முனையம் நேரடியாக மூலத்துடன் இணைக்கப்பட்டுள்ளதுஜி.எஸ்= 0 வி. இது கேட் மற்றும் மூல டெர்மினல்கள் ஒரே மாதிரியான திறனில் இருக்க உதவுகிறது, மேலும் ஒவ்வொரு பி-பொருளின் குறைந்த முடிவின் குறைவு பகுதியிலும் விளைகிறது, மேலே உள்ள முதல் வரைபடத்தில் ஒரு சார்பு இல்லாத நிலையில் நாம் காண்கிறோம்.

ஒரு மின்னழுத்தம் விDD(= விடி.எஸ்) பயன்படுத்தப்படுகிறது, எலக்ட்ரான்கள் வடிகால் முனையத்தை நோக்கி இழுக்கப்படுகின்றன, இது படம் 5.4 இல் சுட்டிக்காட்டப்பட்டுள்ளபடி தற்போதைய ஐடியின் வழக்கமான ஓட்டத்தை உருவாக்குகிறது.

கட்டண ஓட்டத்தின் திசை வடிகால் மற்றும் மூல மின்னோட்டம் அளவில் சமமாக இருப்பதை வெளிப்படுத்துகிறது (I.டி= நான்எஸ்). படம் 5.4 இல் சித்தரிக்கப்பட்டுள்ள நிபந்தனைகளின் படி, கட்டணத்தின் ஓட்டம் மிகவும் கட்டுப்பாடற்றதாகத் தோன்றுகிறது, மேலும் வடிகால் மற்றும் மூலத்திற்கு இடையில் n- சேனலின் எதிர்ப்பால் மட்டுமே பாதிக்கப்படுகிறது.

பி-வகை இரண்டு பொருட்களின் மேல் பகுதியையும் சுற்றி குறைப்பு பகுதி பெரியதாக இருப்பதை நீங்கள் கவனிக்கலாம். பிராந்தியத்தின் அளவிலான இந்த வேறுபாடு படம் 5.5 மூலம் விளக்கப்படுகிறது. N- சேனலில் ஒரு சீரான எதிர்ப்பைக் கொண்டிருப்பதை கற்பனை செய்யலாம், இது படம் 5.5 இல் சுட்டிக்காட்டப்பட்ட பிரிவுகளாகப் பிரிக்கப்படலாம்.

தற்போதைய நான்டிஅதே படத்தில் சுட்டிக்காட்டப்பட்டுள்ளபடி சேனல் வழியாக மின்னழுத்த வரம்புகளை உருவாக்கலாம். இதன் விளைவாக, p- வகை பொருளின் மேல் பகுதி சுமார் 1.5 V அளவிலான தலைகீழ் சார்புடையதாக இருக்கும், கீழ் பகுதி வெறுமனே 0.5 V ஆல் தலைகீழ்-சார்புடையதாக இருக்கும்.

முழு சேனலுடனும் p-n சந்தி தலைகீழ்-சார்புடையது என்பது அதே படத்தில் காட்டப்பட்டுள்ளபடி பூஜ்ஜிய ஆம்பியர்களுடன் ஒரு வாயில் மின்னோட்டத்தை உருவாக்குகிறது. இந்த பண்பு எனக்கு வழிவகுக்கிறதுஜி= 0 A என்பது JFET இன் முக்கியமான பண்பு.

என விடி.எஸ்சாத்தியம் 0 முதல் சில வோல்ட் வரை அதிகரிக்கப்படுகிறது, ஓம் சட்டம் மற்றும் I இன் சதி படி தற்போதைய அதிகரிக்கிறதுடிவரி 5டி.எஸ்படம் 5.6 இல் நிரூபிக்கப்பட்டுள்ளது.

சதித்திட்டத்தின் ஒப்பீட்டு நேர்மை V இன் குறைந்த மதிப்பு பகுதிகளுக்கு என்பதைக் காட்டுகிறதுடி.எஸ், எதிர்ப்பு அடிப்படையில் சீரானது. என விடி.எஸ்படம் 5.6 இல் வி.பி எனப்படும் ஒரு நிலைக்கு உயர்ந்து, நெருங்குகிறது, படம் 5.4 இல் கொடுக்கப்பட்டுள்ளபடி குறைப்பு பகுதிகள் விரிவடைகின்றன.

இது சேனல் அகலத்தை வெளிப்படையாகக் குறைக்கிறது. குறைக்கப்பட்ட கடத்தல் பாதை படம் 5.6 இன் வளைவுக்கு வழிவகுக்கும் எதிர்ப்பின் அதிகரிப்புக்கு வழிவகுக்கிறது.

வளைவு எவ்வளவு கிடைமட்டமாக இருக்கிறதோ, அவ்வளவு உயர்ந்த எதிர்ப்பாகும், இது கிடைமட்ட பிராந்தியத்தில் “எல்லையற்ற” ஓம்களை நோக்கி எதிர்ப்பைப் பெறுகிறது என்பதைக் குறிக்கிறது. போது விடி.எஸ்படம் 5.7 இல் காட்டப்பட்டுள்ளபடி இரண்டு சிதைவு பகுதிகளும் “தொடர்பு” கொள்ளக்கூடும் என்று தோன்றும் அளவிற்கு அதிகரிக்கிறது, இது பிஞ்ச்-ஆஃப் எனப்படும் சூழ்நிலைக்கு வழிவகுக்கிறது.

எந்த அளவு விடி.எஸ்இந்த நிலைமை உருவாகிறது பிஞ்ச்-ஆஃப் மின்னழுத்தம் மற்றும் அது V ஆல் குறிக்கப்படுகிறதுபிபடம் 5.6 இல் வழங்கப்பட்டுள்ளது. பொதுவாக, பிஞ்ச்-ஆஃப் என்ற சொல் தவறாக வழிநடத்துகிறது, ஏனெனில் இது தற்போதைய I ஐ குறிக்கிறதுடிபடம் 5.6 இல் நிரூபிக்கப்பட்டுள்ளபடி, இந்த வழக்கில் இது தெளிவாகத் தெரியவில்லை. நான்டிநான் என வகைப்படுத்தப்படும் ஒரு செறிவு நிலை வைத்திருக்கிறதுடி.எஸ்.எஸ்படம் 5.6 இல்.

உண்மை என்னவென்றால், மிகக் குறைந்த சேனல் தொடர்கிறது, கணிசமாக அதிக செறிவுள்ள மின்னோட்டத்துடன்.

ஐடி கைவிடப்படாத புள்ளி பிஞ்ச்-ஆஃப் படம் 5.6 இல் சுட்டிக்காட்டப்பட்டுள்ளபடி செறிவு அளவைப் பாதுகாக்கிறது பின்வரும் ஆதாரத்துடன் உறுதிப்படுத்தப்பட்டுள்ளது:

வடிகால் மின்னோட்டம் இல்லாததால், பி-என் சந்திப்பில் தலைகீழ் சார்புகளின் மாறிவரும் அளவை தீர்மானிக்க n- சேனல் பொருள் மூலம் மாறுபட்ட சாத்தியமான நிலைகளின் சாத்தியத்தை நீக்குகிறது. இறுதி முடிவு தூண்டப்பட்ட குறைப்பு பகுதி விநியோகத்தை இழந்தது பிஞ்ச்-ஆஃப் தொடங்க.

நாம் வி அதிகரிக்கும்போதுடி.எஸ்மேலே விபி, இரண்டு சிதைவு பகுதிகளும் சேனலுடன் நீளத்தை அதிகரிப்பதை எதிர்கொள்ளும் நெருங்கிய தொடர்பு பகுதி. இருப்பினும் ஐடி நிலை தொடர்ந்து மாறாமல் உள்ளது.

இவ்வாறு கணம் விடி.எஸ்V ஐ விட அதிகமாக உள்ளதுப, தற்போதைய மூலத்தின் பண்புகளை JFET பெறுகிறது.

ஒரு JFET இல் படம் 5.8 இல் நிரூபிக்கப்பட்டுள்ளபடி I இல் தீர்மானிக்கப்படுகிறதுடி= நான்டி.எஸ்.எஸ், ஆனால் மின்னழுத்தம் விடி.எஸ்VP ஐ விட அதிகமாக இணைக்கப்பட்ட சுமை மூலம் நிறுவப்பட்டுள்ளது.

ஐடிஎஸ்எஸ் குறியீட்டைத் தேர்ந்தெடுப்பது வாயிலுக்கு மூலமாக ஒரு குறுகிய சுற்று இணைப்பைக் கொண்ட வடிகால் மூல மூல மின்னோட்டமாகும் என்ற உண்மையை அடிப்படையாகக் கொண்டது.

மேலதிக விசாரணை பின்வரும் மதிப்பீட்டை எங்களுக்கு வழங்குகிறது:

நான்டி.எஸ்.எஸ்இது ஒரு JFET க்கான மிக உயர்ந்த வடிகால் மின்னோட்டமாகும் மற்றும் இது V நிபந்தனைகளால் நிறுவப்பட்டுள்ளதுஜி.எஸ்= 0 வி மற்றும் விடி.எஸ்> | வி.பி |.

படம் 5.6 விஜி.எஸ்வளைவின் முழுமையான நீட்டிப்புக்கு 0 வி ஆகும். பின்வரும் பிரிவுகளில், படம் 5.6 பண்புக்கூறுகள் V இன் அளவாக எவ்வாறு பாதிக்கப்படுகின்றன என்பதைக் கற்றுக்கொள்வோம்ஜி.எஸ்மாறுபட்டது.

விஜி.எஸ் <0V

கேட் மற்றும் மூலத்தின் குறுக்கே பயன்படுத்தப்படும் நிலையற்ற தன்மை VGS என குறிக்கப்படுகிறது, இது JFET செயல்பாடுகளை கட்டுப்படுத்தும் பொறுப்பாகும்.

நான் ஒரு வளைவைப் போலவே, ஒரு பிஜேடியின் உதாரணத்தை எடுத்துக் கொண்டால்சிVs VஇதுI இன் பல்வேறு நிலைகளுக்கு தீர்மானிக்கப்படுகின்றனபி, இதேபோல் நான் வளைவுகள்டிVs Vடி.எஸ்V இன் பல்வேறு நிலைகளுக்குஜி.எஸ்ஒரு JFET எண்ணுக்கு உருவாக்கலாம்.

இதற்காக கேட் முனையம் மூல ஆற்றலின் மட்டத்திற்கு கீழே தொடர்ச்சியான குறைந்த ஆற்றலில் அமைக்கப்பட்டுள்ளது.

கீழே உள்ள Fig.5.9 ஐக் குறிப்பிடுகையில், குறைக்கப்பட்ட V க்கு கேட் / மூல முனையங்கள் முழுவதும் -1 வி பயன்படுத்தப்படுகிறதுடி.எஸ்நிலை.

எதிர்மறை சாத்தியமான சார்பு V இன் நோக்கம்ஜி.எஸ்V இன் நிலைமையை ஒத்த குறைப்பு பகுதிகளை உருவாக்குவதாகும்ஜி.எஸ்= 0, ஆனால் கணிசமாகக் குறைக்கப்பட்ட விடி.எஸ்.

இது குறைந்த அளவிலான V உடன் செறிவூட்டல் புள்ளியை அடைய வாயிலை ஏற்படுத்துகிறதுடி.எஸ்படம் 5.10 (விஜி.எஸ்= -1 வி).

I க்கான தொடர்புடைய நிறைவு நிலைடிகுறைக்கப்படுவதைக் காணலாம் மற்றும் உண்மையில் V ஆக குறைந்து கொண்டே செல்கிறதுஜி.எஸ்மேலும் எதிர்மறையாக செய்யப்படுகிறது.

படம் 5.10 இல் பிஞ்ச்-ஆஃப் மின்னழுத்தம் V என ஒரு பரவளைய வடிவத்துடன் கைவிடுவதை எவ்வாறு தெளிவாகக் காணலாம்ஜி.எஸ்மேலும் மேலும் எதிர்மறையாகிறது.

இறுதியாக, விஜி.எஸ்= -விப, இது ஒரு செறிவு அளவை நிறுவ போதுமான எதிர்மறையைப் பெறுகிறது, இது இறுதியில் 0 mA ஆகும். இந்த மட்டத்தில், JFET முற்றிலும் 'முடக்கப்பட்டுள்ளது'.

வி நிலைஜி.எஸ்இது எனக்கு காரணமாகிறதுடி0 mA ஐ அடைய V ஆல் வகைப்படுத்தப்படுகிறதுஜி.எஸ்= விபி, இதில் விபிn- சேனல் சாதனங்களுக்கான எதிர்மறை மின்னழுத்தம் மற்றும் p- சேனல் JFET களுக்கான நேர்மறை மின்னழுத்தமாகும்.

பொதுவாக, நீங்கள் காண்பிக்கும் பெரும்பாலான JFET தரவுத்தாள்களைக் காணலாம் பிஞ்ச்-ஆஃப் V என குறிப்பிடப்பட்ட மின்னழுத்தம்ஜி.எஸ் (ஆஃப்)V க்கு பதிலாகபி.

மேலே உள்ள படத்தில் பிஞ்ச்-ஆஃப் லோகஸின் வலது புறத்தில் உள்ள பகுதி என்பது விலகல் இலவச சமிக்ஞையை அடைவதற்கு நேரியல் பெருக்கிகளில் வழக்கமாக பயன்படுத்தப்படும் இடம். இந்த பகுதி பொதுவாக அழைக்கப்படுகிறது நிலையான-மின்னோட்ட, செறிவு அல்லது நேரியல் பெருக்கம் பகுதி.

மின்னழுத்த கட்டுப்பாட்டு மின்தடையம்

அதே உருவத்தில் பிஞ்ச்-ஆஃப் லோகஸின் இடது பக்கத்தில் இருக்கும் பகுதி, என அழைக்கப்படுகிறது ஓமிக் பகுதி அல்லது மின்னழுத்தத்தால் கட்டுப்படுத்தப்பட்ட எதிர்ப்பு பகுதி.

இந்த பிராந்தியத்தில் சாதனம் உண்மையில் ஒரு மாறி மின்தடையாக இயக்கப்படலாம் (எடுத்துக்காட்டாக தானியங்கி ஆதாயக் கட்டுப்பாட்டு பயன்பாட்டில்), அதன் எதிர்ப்பை பயன்பாட்டு வாயில் / மூல ஆற்றல் மூலம் கட்டுப்படுத்தலாம்.

V க்கான JFET இன் வடிகால் / மூல எதிர்ப்பைக் குறிக்கும் ஒவ்வொரு வளைவுகளின் சாய்வையும் நீங்கள் காணலாம்டி.எஸ்

எதிர்மறை ஆற்றலுடன் வி.ஜி.எஸ்ஸை நாம் அதிகமாக்கும்போது, ஒவ்வொரு வளைவின் சாய்வும் மேலும் மேலும் கிடைமட்டமாகி, விகிதாசாரமாக அதிகரிக்கும் எதிர்ப்பு நிலைகளை வெளிப்படுத்துகிறது.

விஜிஎஸ் மின்னழுத்தத்தைப் பொறுத்து, எதிர்ப்பின் நிலைக்கு ஒரு நல்ல ஆரம்ப தோராயத்தை பின்வரும் சமன்பாட்டின் மூலம் பெற முடிகிறது.

p-Channel JFET வேலை

பி-சேனல் JFET இன் உள் தளவமைப்பு மற்றும் கட்டுமானம் துல்லியமாக n- சேனல் எண்ணுடன் ஒத்திருக்கிறது, தவிர p- மற்றும் n- வகை பொருட்கள் பகுதிகள் தலைகீழாக மாற்றப்பட்டுள்ளன, கீழே காட்டப்பட்டுள்ளபடி:

மின்னழுத்த விஜிஎஸ் மற்றும் விடிஎஸ் ஆகியவற்றின் உண்மையான துருவமுனைப்புகளுடன், தற்போதைய ஓட்டத்தின் திசைகளும் தலைகீழாக இருப்பதைக் காணலாம். பி-சேனல் JFET இன் விஷயத்தில், கேட் / மூலத்தில் நேர்மறையான திறனை அதிகரிப்பதன் மூலம் சேனல் கட்டுப்படுத்தப்படும்.

V க்கான இரட்டை சந்தாவுடன் குறியீடுடி.எஸ்V க்கு எதிர்மறை மின்னழுத்தத்திற்கு வழிவகுக்கும்டி.எஸ், படம் 5.12 இன் பண்புகளில் காட்டப்பட்டுள்ளது. இங்கே, நீங்கள் என்னைக் காணலாம்டி.எஸ்.எஸ்6 mA இல், V இல் ஒரு பிஞ்ச்-ஆஃப் மின்னழுத்தம்ஜி.எஸ்= + 6 வி.

V க்கான மைனஸ் அடையாளம் உன்னால் தயவுசெய்து குழப்பமடைய வேண்டாம்டி.எஸ். மூலமானது வடிகால் விட அதிக ஆற்றலைக் கொண்டுள்ளது என்பதை இது குறிக்கிறது.

உயர் V க்கான வளைவுகள் இருப்பதை நீங்கள் காணலாம்டி.எஸ்அளவுகள் தடையின்றி மதிப்புகளுக்கு உயர்கின்றன. செங்குத்தாக சுட்டிக்காட்டப்பட்ட உயர்வு ஒரு முறிவு சூழ்நிலையை குறிக்கிறது, அதாவது சேனல் சாதனம் வழியாக மின்னோட்டம் இந்த நேரத்தில் வெளிப்புற சுற்றுகளால் முழுமையாக கட்டுப்படுத்தப்படுகிறது.

N- சேனல் சாதனத்திற்கான படம் 5.10 இல் இது வெளிப்படையாகத் தெரியவில்லை என்றாலும், இது போதுமான உயர் மின்னழுத்தத்தின் கீழ் சாத்தியமாக இருக்கலாம்.

வி என்றால் இந்த பகுதியை அகற்றலாம்டி.எஸ் (அதிகபட்சம்)சாதனத்தின் தரவுத்தாள் இருந்து குறிப்பிடப்பட்டுள்ளது, மேலும் சாதனம் உண்மையான விடி.எஸ்எந்த V க்கும் இந்த குறிப்பிடப்பட்ட மதிப்பை விட மதிப்பு குறைவாக உள்ளதுஜி.எஸ்.

முந்தைய: 5 சிறந்த 40 வாட் பெருக்கி சுற்றுகள் ஆராயப்பட்டன அடுத்து: 2N3055 தரவுத்தாள், பின்அவுட், பயன்பாட்டு சுற்றுகள்