இந்த இடுகையில் நாம் என்ன தர்க்க வாயில்கள் மற்றும் அதன் செயல்பாடுகள் குறித்து விரிவாக புரிந்து கொள்ளப் போகிறோம். அடிப்படை வரையறை, சின்னம், உண்மை அட்டவணை, மல்டி உள்ளீட்டு வாயில்கள் ஆகியவற்றைப் பார்ப்போம், நாங்கள் டிரான்சிஸ்டர் அடிப்படையிலான கேட் சமமானவற்றையும் உருவாக்குவோம், இறுதியாக பல்வேறு தொடர்புடைய CMOS ஐசிகளைப் பற்றிய ஒரு கண்ணோட்டத்தை எடுப்போம்.

லாஜிக் கேட்ஸ் என்றால் என்ன

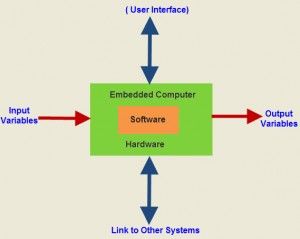

எலக்ட்ரானிக் சர்க்யூட்டில் ஒரு லாஜிக் கேட் ஒரு பூலியன் செயல்பாட்டின் மூலம் குறிப்பிடப்படும் ஒரு உடல் அலகு என வெளிப்படுத்தப்படலாம்.

வேறு வார்த்தைகளில் கூறுவதானால், ஒரு தர்க்கரீதியான செயல்பாட்டை ஒற்றை அல்லது அதற்கு மேற்பட்ட பைனரி உள்ளீடுகளைப் பயன்படுத்தி இயக்க மற்றும் ஒரு பைனரி வெளியீட்டை உருவாக்க ஒரு லாஜிக் கேட் வடிவமைக்கப்பட்டுள்ளது.

எலக்ட்ரானிக் லாஜிக் வாயில்கள் அடிப்படையில் கட்டமைக்கப்பட்டு செயல்படுத்தப்படுகின்றன, அவை குறைக்கடத்தி தொகுதிகள் அல்லது டையோட்கள் அல்லது டிரான்சிஸ்டர்கள் போன்ற உறுப்புகளைப் பயன்படுத்தி நன்கு வரையறுக்கப்பட்ட சுவிட்ச் முறையைக் கொண்ட ஆன் / ஆஃப் சுவிட்சுகள் போல வேலை செய்கின்றன. லாஜிக் வாயில்கள் பூலியன் செயல்பாடுகளின் தொகுப்பை எளிதில் செயல்படுத்தும் வாயில்களின் அடுக்கை எளிதாக்குகின்றன, இதனால் அனைத்து பூலியன் தர்க்கங்களின் இயற்பியல் மாதிரிகளையும் உருவாக்க முடியும். இது பூலியன் தர்க்கத்தைப் பயன்படுத்தி எழுதக்கூடிய வழிமுறைகள் மற்றும் கணிதத்தை மேலும் செயல்படுத்துகிறது.

லாஜிக் சுற்றுகள் மல்டிப்ளெக்சர்கள், பதிவேடுகள், எண்கணித லாஜிக் அலகுகள் (ALU கள்) மற்றும் கணினி நினைவகம் மற்றும் நுண்செயலிகளின் வரம்பில் குறைக்கடத்தி கூறுகளைப் பயன்படுத்தலாம், இதில் 100 மில்லியனுக்கும் அதிகமான லாஜிக் வாயில்கள் உள்ளன. இன்றைய செயல்பாட்டில், நீங்கள் பெரும்பாலும் புலம்-விளைவு டிரான்சிஸ்டர்களை (FET கள்) காணலாம், அவை தர்க்க வாயில்களை உற்பத்தி செய்வதற்குப் பயன்படுத்தப்படுகின்றன, இதற்கு ஒரு சிறந்த உதாரணம் மெட்டல்-ஆக்சைடு-குறைக்கடத்தி புலம்-விளைவு டிரான்சிஸ்டர்கள் அல்லது MOSFET கள்.

தர்க்கம் மற்றும் வாயில்களுடன் டுடோரியலைத் தொடங்குவோம்.

லாஜிக் “மற்றும்” கேட் என்றால் என்ன?

இது ஒரு மின்னணு வாயில் ஆகும், அதன் வெளியீடு “உயர்” அல்லது “1” அல்லது “உண்மை” ஆக மாறுகிறது அல்லது AND வாயில்களின் அனைத்து உள்ளீடுகளும் “உயர்” அல்லது “1” அல்லது “உண்மை” அல்லது “ நேர்மறை சமிக்ஞை ”.

எடுத்துக்காட்டு: எல்லா உள்ளீடுகளும் “உயர்ந்ததாக” இருந்தால், ‘n’ எண்ணிக்கையிலான உள்ளீடுகளைக் கொண்ட AND வாயிலில் சொல்லுங்கள் வெளியீடு “உயர்” ஆக மாறும். ஒரு உள்ளீடு “குறைந்த” அல்லது “0” அல்லது “பொய்” அல்லது “எதிர்மறை சமிக்ஞை” என்றாலும், வெளியீடு “குறைந்த” அல்லது “0” அல்லது “பொய்” ஆக மாறும் அல்லது “எதிர்மறை சமிக்ஞையை” அளிக்கிறது.

குறிப்பு:

“உயர்”, “1”, “நேர்மறை சமிக்ஞை”, “உண்மை” என்ற சொல் அடிப்படையில் ஒரே மாதிரியானவை (நேர்மறை சமிக்ஞை என்பது பேட்டரி அல்லது மின்சாரம் வழங்கலின் நேர்மறை சமிக்ஞை).

“குறைந்த”, “0”, “எதிர்மறை சமிக்ஞை”, “பொய்” என்ற சொல் அடிப்படையில் ஒன்றே (எதிர்மறை சமிக்ஞை என்பது பேட்டரி அல்லது மின்சாரம் எதிர்மறை சமிக்ஞை).

லாஜிக் மற்றும் கேட் சின்னத்தின் விளக்கம்:

இங்கே “A” மற்றும் “B” இரண்டு உள்ளீடுகள் மற்றும் “Y” வெளியீடு.

தர்க்கம் மற்றும் வாயிலுக்கான பூலியன் வெளிப்பாடு: ‘Y’ வெளியீடு ‘A’ மற்றும் ‘B’ ஆகிய இரண்டு உள்ளீடுகளின் பெருக்கமாகும். (A.B) = Y.

பூலியன் பெருக்கல் ஒரு புள்ளியால் குறிக்கப்படுகிறது (.)

‘A’ என்பது ‘1’ மற்றும் ‘B’ என்பது ‘1’ என்றால் வெளியீடு (A.B) = 1 x 1 = ‘1’ அல்லது “high”

‘A’ என்பது ‘0’ மற்றும் ‘B’ ‘1’ என்றால் வெளியீடு (A.B) = 0 x 1 = ‘0’ அல்லது “Low”

‘A’ என்பது ‘1’ மற்றும் ‘B’ என்பது ‘0’ என்றால் வெளியீடு (A.B) = 1 x 0 = ‘0’ அல்லது “Low”

‘A’ என்பது ‘0’ மற்றும் ‘B’ என்பது ‘0’ என்றால் வெளியீடு (A.B) = 0 x 0 = ‘0’ அல்லது “Low”

மேற்கண்ட நிபந்தனைகள் உண்மை அட்டவணையில் எளிமைப்படுத்தப்பட்டுள்ளன.

உண்மை அட்டவணை (இரண்டு உள்ளீடு):

| ஒரு (உள்ளீடு) | பி (INPUT) | ஒய் (வெளியீடு) |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

3-உள்ளீடு “மற்றும்” கேட்:

3 உள்ளீடு மற்றும் வாயிலின் விளக்கம்:

தர்க்கம் மற்றும் வாயில்கள் ‘n’ எண்ணிக்கையிலான உள்ளீடுகளைக் கொண்டிருக்கலாம், அதாவது இது இரண்டுக்கும் மேற்பட்ட உள்ளீடுகளைக் கொண்டிருக்கலாம் (லாஜிக் மற்றும் வாயில்களில் குறைந்தது இரண்டு உள்ளீடு மற்றும் எப்போதும் ஒரு வெளியீடு இருக்கும்).

3 உள்ளீடு மற்றும் வாயிலுக்கு பூலியன் சமன்பாடு இப்படி மாறுகிறது: (A.B.C) = Y, இதேபோல் 4 உள்ளீடு மற்றும் அதற்கு மேல்.

3 உள்ளீட்டு தர்க்கம் மற்றும் வாயிலுக்கான உண்மை அட்டவணை:

| A (INPUT) | பி (INPUT) | சி (INPUT) | ஒய் (வெளியீடு) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

பல உள்ளீட்டு தர்க்கம் மற்றும் வாயில்கள்:

வணிக ரீதியாக கிடைக்கக்கூடிய லாஜிக் மற்றும் வாயில்கள் 2, 3 மற்றும் 4 உள்ளீடுகளில் மட்டுமே கிடைக்கின்றன. எங்களிடம் 4 க்கும் மேற்பட்ட உள்ளீடு இருந்தால், நாங்கள் வாயில்களை அடுக்க வேண்டும்.

2 உள்ளீடு மற்றும் வாயில்களை பின்வருமாறு அடுக்கி வைப்பதன் மூலம் ஆறு உள்ளீட்டு தர்க்கம் மற்றும் வாயில்களை நாம் கொண்டிருக்கலாம்:

இப்போது மேலே உள்ள சுற்றுக்கான பூலியன் சமன்பாடு Y = (A.B) ஆகிறது. (C.D). (E.F)

இன்னும், குறிப்பிடப்பட்ட அனைத்து தருக்க விதிகளும் மேலே உள்ள சுற்றுக்கு பொருந்தும்.

மேலே உள்ள 6 உள்ளீடுகள் மற்றும் வாயில்களிலிருந்து 5 உள்ளீடுகளை மட்டுமே நீங்கள் பயன்படுத்தப் போகிறீர்கள் என்றால், எந்த ஒரு முனையிலும் ஒரு இழுக்கும்-மின்தடையத்தை நாங்கள் இணைக்க முடியும், இப்போது அது 5 உள்ளீடு மற்றும் வாயிலாக மாறும்.

டிரான்சிஸ்டர் அடிப்படையிலான இரண்டு உள்ளீடு லாஜிக் மற்றும் கேட்:

இப்போது எங்களுக்குத் தெரியும், ஒரு தர்க்கம் மற்றும் வாயில் எவ்வாறு செயல்படுகிறது, இரண்டு NPN டிரான்சிஸ்டர்களைப் பயன்படுத்தி 2 உள்ளீடு மற்றும் வாயிலை உருவாக்குவோம். லாஜிக் ஐ.சிக்கள் கிட்டத்தட்ட அதே வழியில் கட்டப்பட்டுள்ளன.

இரண்டு டிரான்சிஸ்டர் மற்றும் கேட் திட்ட:

“Y” வெளியீட்டில் எல்.ஈ.டி அதிகமாக இருந்தால் எல்.ஈ.டி ஒளிரும் (எல்.ஈ.டி + வீ டெர்மினல் “ஒய்” இல் 330 ஓம் மின்தடையுடன் மற்றும் ஜிஎன்டிக்கு எதிர்மறையானது).

இரண்டு டிரான்சிஸ்டர்களின் அடிப்பகுதிக்கு நாம் உயர் சமிக்ஞையைப் பயன்படுத்தும்போது, இரண்டு டிரான்சிஸ்டர்களும் இயக்கப்படும், + 5 வி சிக்னல் T2 இன் உமிழ்ப்பில் கிடைக்கும், இதனால் வெளியீடு அதிகமாக மாறும்.

டிரான்சிஸ்டரில் ஏதேனும் ஒன்று முடக்கப்பட்டிருந்தால், டி 2 உமிழ்ப்பில் நேர்மறை மின்னழுத்தம் கிடைக்காது, ஆனால் 1 கே புல் டவுன் மின்தடையின் காரணமாக எதிர்மறை மின்னழுத்தம் வெளியீட்டில் கிடைக்கும், எனவே வெளியீடு குறைவாக குறிப்பிடப்படுகிறது.

உங்கள் சொந்த தர்க்கத்தையும் வாயிலையும் எவ்வாறு உருவாக்குவது என்பது இப்போது உங்களுக்குத் தெரியும்.

குவாட் மற்றும் கேட் ஐசி 7408:

நீங்கள் சந்தையில் இருந்து லாஜிக் மற்றும் கேட்டை வாங்க விரும்பினால், மேலே உள்ளமைவில் நீங்கள் பெறுவீர்கள்.

இது 14 ஊசிகளைக் கொண்டுள்ளது முள் # 7 மற்றும் முள் # 14 முறையே ஜிஎன்டி மற்றும் விசிசி. இது 5 வி இல் இயக்கப்படுகிறது.

பரப்புதல் தாமதம்:

பரப்புதல் தாமதம் என்பது வெளியீடு குறைந்த அளவிலிருந்து உயர் மற்றும் அதற்கு நேர்மாறாக மாறுவதற்கு எடுக்கப்பட்ட நேரம்.

LOW முதல் HIGH வரை பரப்புதல் தாமதம் 27 நானோ விநாடிகள்.

HIGH முதல் LOW வரை பரப்புதல் தாமதம் 19 நானோ விநாடிகள்.

பொதுவாக கிடைக்கக்கூடிய பிற “மற்றும்” கேட் ஐசிக்கள்:

L 74LS08 குவாட் 2-உள்ளீடு

L 74LS11 டிரிபிள் 3-உள்ளீடு

L 74LS21 இரட்டை 4-உள்ளீடு

40 CD4081 குவாட் 2-உள்ளீடு

40 CD4073 டிரிபிள் 3-உள்ளீடு

40 CD4082 இரட்டை 4-உள்ளீடு

மேலும் தகவலுக்கு மேலே உள்ள ஐ.சி.களுக்கான தரவு தாளை நீங்கள் எப்போதும் பார்க்கலாம்.

எப்படி தர்க்கம் “பிரத்யேக NOR” கேட் செயல்பாடு

இந்த இடுகையில் நாம் தர்க்கம் “Ex-NOR” வாயில் அல்லது பிரத்தியேக- NOR வாயில் பற்றி ஆராயப்போகிறோம். அடிப்படை வரையறை, சின்னம், உண்மை அட்டவணை, முன்னாள் NOR சமமான சுற்று, முன்னாள் NOR உணர்தல் ஆகியவற்றைப் பார்ப்போம் தர்க்கம் NAND வாயில்கள் இறுதியாக, குவாட் 2 உள்ளீடு எக்ஸ்-ஓஆர் கேட் ஐசி 74266 பற்றிய கண்ணோட்டத்தை எடுப்போம்.

“பிரத்தியேக NOR” வாயில் என்றால் என்ன?

இது ஒரு மின்னணு வாயில் ஆகும், அதன் வெளியீடு “உயர்” அல்லது “1” அல்லது “உண்மை” ஆக மாறுகிறது அல்லது உள்ளீடுகள் கூட தர்க்கம் “1 கள்” (அல்லது “உண்மை” அல்லது “உயர்” அல்லது “ நேர்மறை சமிக்ஞை ”).

எடுத்துக்காட்டு: உள்ளீடுகள் 2 அல்லது 4 அல்லது 6 உள்ளீடுகளுடன் தர்க்கம் “உயரம்” என்றால் (உள்ளீடு “1 வி” கூட) வெளியீடு “உயர்” ஆக மாறும் போது, ‘என்’ உள்ளீடுகளின் எண்ணிக்கையுடன் ஒரு பிரத்யேக என்.ஓ.ஆர் கேட் சொல்லுங்கள்.

உள்ளீட்டு ஊசிகளுக்கு (அதாவது 'உயர்' தர்க்கம் 'உயர்' மற்றும் அனைத்து தர்க்கமும் 'குறைந்த') எந்த தர்க்கத்தையும் நாங்கள் பயன்படுத்தாவிட்டாலும், இன்னும் 'பூஜ்ஜியம்' என்பது வெளியீடு 'உயர்' ஆக மாறும் சம எண்ணாகும்.

பயன்படுத்தப்படும் '1 வி' தர்க்கத்தின் எண்ணிக்கை ODD ஆக இருந்தால், வெளியீடு 'குறைந்த' (அல்லது '0' அல்லது 'தவறான' அல்லது 'எதிர்மறை சமிக்ஞை') ஆக மாறும்.

இது தர்க்கம் “பிரத்தியேக OR” வாயிலுக்கு எதிரானது, அங்கு உள்ளீடுகள் தர்க்கத்தின் ODD எண் “1s” ஆக இருக்கும்போது அதன் வெளியீடு “HIGH” ஆக மாறும்.

குறிப்பு:

“உயர்”, “1”, “நேர்மறை சமிக்ஞை”, “உண்மை” என்ற சொல் அடிப்படையில் ஒரே மாதிரியானவை (நேர்மறை சமிக்ஞை என்பது பேட்டரி அல்லது மின்சாரம் வழங்கலின் நேர்மறை சமிக்ஞை).

“குறைந்த”, “0”, “எதிர்மறை சமிக்ஞை”, “பொய்” என்ற சொல் அடிப்படையில் ஒன்றே (எதிர்மறை சமிக்ஞை என்பது பேட்டரி அல்லது மின்சாரம் எதிர்மறை சமிக்ஞை).

தர்க்கத்தின் விளக்கம் “பிரத்தியேக NOR” வாயில்:

“பிரத்தியேக NOR” வாயில் சமமான சுற்று:

மேலே உள்ளவை தர்க்கம் Ex-NOR க்கு சமமான சுற்று ஆகும், இது அடிப்படையில் தர்க்கம் “பிரத்தியேக OR” வாயில் மற்றும் தர்க்கம் “NOT” வாயில் ஆகியவற்றின் கலவையாகும்.

இங்கே “A” மற்றும் “B” இரண்டு உள்ளீடுகள் மற்றும் “Y” வெளியீடு.

தர்க்கத்திற்கான பூலியன் வெளிப்பாடு Ex-NOR வாயில்: Y = (AB) ̅ + AB.

‘A’ என்பது ‘1’ மற்றும் ‘B’ என்பது ‘1’ என்றால் வெளியீடு ((AB) ̅ + AB) = 0 + 1 = ‘1’ அல்லது “HIGH”

‘A’ என்பது ‘0’ மற்றும் ‘B’ ‘1’ என்றால் வெளியீடு ((AB) ̅ + AB) = 0 + 0 = ‘0’ அல்லது “LOW”

‘A’ என்பது ‘1’ மற்றும் ‘B’ என்பது ‘0’ என்றால் வெளியீடு ((AB) ̅ + AB) = 0 + 0 = ‘0’ அல்லது “LOW”

‘A’ என்பது ‘0’ மற்றும் ‘B’ என்பது ‘0’ என்றால் வெளியீடு ((AB) ̅ + AB) = 1 + 1 = ‘1’ அல்லது “HIGH”

மேற்கண்ட நிபந்தனைகள் உண்மை அட்டவணையில் எளிமைப்படுத்தப்பட்டுள்ளன.

உண்மை அட்டவணை (இரண்டு உள்ளீடு):

| ஒரு (உள்ளீடு) | பி (INPUT) | ஒய் (வெளியீடு) |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

3 உள்ளீட்டு பிரத்யேக NOR கேட்:

3 உள்ளீட்டின் விளக்கம் Ex-NOR வாயில்:

3 உள்ளீட்டு தர்க்கத்திற்கான உண்மை அட்டவணை EX-OR வாயில்:

| A (INPUT) | பி (INPUT) | சி (INPUT) | ஒய் (வெளியீடு) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

3 உள்ளீட்டு Ex-NOR வாயிலுக்கு பூலியன் சமன்பாடு ஆகிறது: A ̅ (BC) ̅ + ABC ̅ + AB C + A ̅BC.

தர்க்கம் “Ex-NOR” வாயில் ஒரு அடிப்படை தர்க்க வாயில் அல்ல, ஆனால் வெவ்வேறு தர்க்க வாயில்களின் கலவையாகும். தர்க்கம் “அல்லது” வாயில்கள், தர்க்கம் “மற்றும்” வாயில் மற்றும் தர்க்கம் “NAND” வாயில் ஆகியவற்றைப் பயன்படுத்தி Ex-NOR வாயிலை பின்வருமாறு உணர முடியும்:

“பிரத்தியேக NOR” வாயிலுக்கு சமமான சுற்று:

மேலே உள்ள வடிவமைப்பு பெரிய குறைபாட்டைக் கொண்டுள்ளது, ஒரு முன்னாள் NOR வாயிலை உருவாக்க எங்களுக்கு 3 வெவ்வேறு தர்க்க வாயில்கள் தேவை. ஆனால் முன்னாள் NOR வாயிலை தர்க்கரீதியான “NAND” வாயில்களுடன் மட்டுமே செயல்படுத்துவதன் மூலம் இந்த சிக்கலை நாம் சமாளிக்க முடியும், இது புனையப்படுவதற்கும் சிக்கனமானது.

NAND வாயிலைப் பயன்படுத்தி பிரத்யேக NOR வாயில்:

எண்கணித செயல்பாடுகள், பைனரி சேர்ப்பவர்கள், பைனரி கழித்தல், பரிதி சரிபார்ப்புகள் போன்ற சிக்கலான கணினி பணிகளைச் செய்ய பிரத்யேக NOR வாயில்கள் பயன்படுத்தப்படுகின்றன, அவை டிஜிட்டல் ஒப்பீட்டாளர்களாகப் பயன்படுத்தப்படுகின்றன.

லாஜிக் பிரத்தியேக-என்ஓஆர் கேட் ஐசி 74266:

நீங்கள் சந்தையில் இருந்து லாஜிக் எக்ஸ்-என்ஆர் கேட்டை வாங்க விரும்பினால், மேலே உள்ள டிஐபி உள்ளமைவைப் பெறுவீர்கள்.

இது 14 ஊசிகளைக் கொண்டுள்ளது முள் # 7 மற்றும் முள் # 14 முறையே ஜிஎன்டி மற்றும் விசிசி. இது 5 வி இல் இயக்கப்படுகிறது.

பரப்புதல் தாமதம்:

பரப்புதல் தாமதம் என்பது வெளியீடு LOW இலிருந்து HIGH ஆகவும், உள்ளீட்டைக் கொடுத்த பிறகு நேர்மாறாகவும் மாறுவதற்கு எடுக்கப்பட்ட நேரம்.

LOW முதல் HIGH வரை பரப்புதல் தாமதம் 23 நானோ விநாடிகள்.

HIGH முதல் LOW வரை பரப்புதல் தாமதம் 23 நானோ விநாடிகள்.

பொதுவாக கிடைக்கும் “EX-NOR” கேட் ஐசிக்கள்:

74LS266 குவாட் 2-உள்ளீடு

CD4077 குவாட் 2-உள்ளீடு

NAND கேட் எவ்வாறு இயங்குகிறது

கீழேயுள்ள விளக்கத்தில் டிஜிட்டல் லாஜிக் NAND கேட் பற்றி ஆராயப்போகிறோம். அடிப்படை வரையறை, சின்னம், உண்மை அட்டவணை, மல்டி உள்ளீடு NAND கேட் ஆகியவற்றைப் பார்ப்போம், டிரான்சிஸ்டர் அடிப்படையிலான 2 உள்ளீட்டு NAND வாயில், NAND வாயிலை மட்டுமே பயன்படுத்தி பல்வேறு தர்க்க வாயில்களை உருவாக்குவோம், இறுதியாக NAND வாயில் ஒரு கண்ணோட்டத்தை எடுப்போம் ஐசி 7400.

லாஜிக் “NAND” கேட் என்றால் என்ன?

இது ஒரு மின்னணு வாயில் ஆகும், அதன் வெளியீடு “குறைந்த” அல்லது “0” அல்லது “பொய்” ஆக மாறும் அல்லது NAND வாயில்களின் அனைத்து உள்ளீடுகளும் “உயர்” அல்லது “1” அல்லது “உண்மை” அல்லது “ நேர்மறை சமிக்ஞை ”.

எடுத்துக்காட்டாக: ‘n’ எண்ணிக்கையிலான உள்ளீடுகளைக் கொண்ட ஒரு NAND வாயிலைச் சொல்லுங்கள், எல்லா உள்ளீடுகளும் “உயர்ந்ததாக” இருந்தால் வெளியீடு “LOW” ஆக மாறும். ஒரு உள்ளீடு “குறைந்த” அல்லது “0” அல்லது “தவறான” அல்லது “எதிர்மறை சமிக்ஞை” என்றாலும், வெளியீடு “உயர்” அல்லது “1” அல்லது “உண்மை” ஆக மாறுகிறது அல்லது “நேர்மறை சமிக்ஞையை” அளிக்கிறது.

குறிப்பு:

“உயர்”, “1”, “நேர்மறை சமிக்ஞை”, “உண்மை” என்ற சொல் அடிப்படையில் ஒரே மாதிரியானவை (நேர்மறை சமிக்ஞை என்பது பேட்டரி அல்லது மின்சாரம் வழங்கலின் நேர்மறை சமிக்ஞை).

“குறைந்த”, “0”, “எதிர்மறை சமிக்ஞை”, “பொய்” என்ற சொல் அடிப்படையில் ஒன்றே (எதிர்மறை சமிக்ஞை என்பது பேட்டரி அல்லது மின்சாரம் எதிர்மறை சமிக்ஞை).

லாஜிக் NAND கேட் சின்னத்தின் விளக்கம்:

இங்கே “A” மற்றும் “B” இரண்டு உள்ளீடுகள் மற்றும் “Y” வெளியீடு.

இந்த சின்னம் “மற்றும்” தலைகீழ் “ஓ” வாயில்.

தர்க்கம் “NAND” கேட் சமமான சுற்று:

லாஜிக் NAND கேட் என்பது தர்க்கம் “AND” கேட் மற்றும் லாஜிக் “NOT” கேட் ஆகியவற்றின் கலவையாகும்.

தர்க்க NAND வாயிலுக்கான பூலியன் வெளிப்பாடு: ‘Y’ வெளியீடு ‘A’ மற்றும் ‘B’ ஆகிய இரண்டு உள்ளீடுகளின் நிரப்பு பெருக்கமாகும். Y = ((A.B))

பூலியன் பெருக்கல் ஒரு புள்ளி (.) ஆல் குறிக்கப்படுகிறது மற்றும் நிரப்பு (தலைகீழ்) ஒரு எழுத்தின் மேல் ஒரு பட்டியில் (-) குறிக்கப்படுகிறது.

‘A’ என்பது ‘1’ மற்றும் ‘B’ என்பது ‘1’ என்றால் வெளியீடு ((A.B) ̅) = (1 x 1) ̅ = ‘0’ அல்லது “LOW”

‘A’ என்பது ‘0’ மற்றும் ‘B’ ‘1’ என்றால் வெளியீடு ((A.B) ̅) = (0 x 1) ̅ = ‘1’ அல்லது “HIGH”

‘A’ என்பது ‘1’ மற்றும் ‘B’ என்பது ‘0’ என்றால் வெளியீடு ((A.B) ̅) = (1 x 0) ̅ = ‘1’ அல்லது “HIGH”

‘A’ என்பது ‘0’ மற்றும் ‘B’ என்பது ‘0’ என்றால் வெளியீடு ((A.B) ̅) = (0 x 0) ̅ = ‘1’ அல்லது “HIGH”

மேற்கண்ட நிபந்தனைகள் உண்மை அட்டவணையில் எளிமைப்படுத்தப்பட்டுள்ளன.

உண்மை அட்டவணை (இரண்டு உள்ளீடு):

| ஒரு (உள்ளீடு) | பி (INPUT) | ஒய் (வெளியீடு) |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

3-உள்ளீடு “NAND” கேட்:

3 உள்ளீட்டு NAND வாயிலின் விளக்கம்:

லாஜிக் NAND வாயில்கள் ‘n’ எண்ணிக்கையிலான உள்ளீடுகளைக் கொண்டிருக்கலாம், அதாவது இது இரண்டுக்கும் மேற்பட்ட உள்ளீடுகளைக் கொண்டிருக்கலாம்

(லாஜிக் NAND வாயில்களில் குறைந்தது இரண்டு உள்ளீடு மற்றும் எப்போதும் ஒரு வெளியீடு இருக்கும்).

3 உள்ளீட்டு NAND வாயிலுக்கு பூலியன் சமன்பாடு இப்படி மாறுகிறது: ((A.B.C) ̅) = Y, இதேபோல் 4 உள்ளீடு மற்றும் அதற்கு மேல்.

உண்மை அட்டவணை3 உள்ளீட்டு தர்க்க NAND வாயிலுக்கு:

| A (INPUT) | பி (INPUT) | சி (INPUT) | ஒய் (வெளியீடு) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

பல உள்ளீட்டு தர்க்கம் NAND வாயில்கள்:

வணிக ரீதியாக கிடைக்கக்கூடிய லாஜிக் NAND வாயில்கள் 2, 3 மற்றும் 4 உள்ளீடுகளில் மட்டுமே கிடைக்கின்றன. எங்களிடம் 4 க்கும் மேற்பட்ட உள்ளீடு இருந்தால், நாங்கள் வாயில்களை அடுக்க வேண்டும்.

எடுத்துக்காட்டாக, 5 இரண்டு உள்ளீட்டு NAND வாயில்களை பின்வருமாறு அடுக்கி நான்கு உள்ளீட்டு தர்க்க NAND வாயிலைக் கொண்டிருக்கலாம்:

இப்போது மேலே உள்ள சுற்றுக்கான பூலியன் சமன்பாடு Y = ((A.B.C.D) becomes ஆக மாறுகிறது

இன்னும், குறிப்பிடப்பட்ட அனைத்து தருக்க விதிகளும் மேலே உள்ள சுற்றுக்கு பொருந்தும்.

மேலேயுள்ள 4 உள்ளீடுகள் NAND வாயிலிலிருந்து 3 உள்ளீடுகளை மட்டுமே நீங்கள் பயன்படுத்தப் போகிறீர்கள் என்றால், எந்த ஒரு முனையுடனும் ஒரு இழுக்கும்-மின்தடையத்தை நாங்கள் இணைக்க முடியும், இப்போது அது 3 உள்ளீட்டு NAND வாயிலாக மாறுகிறது.

டிரான்சிஸ்டர் அடிப்படையிலான இரண்டு உள்ளீடு லாஜிக் NAND கேட்:

இப்போது நமக்குத் தெரியும், ஒரு தர்க்கம் NAND கேட் எவ்வாறு செயல்படுகிறது, இரண்டைப் பயன்படுத்தி 2 உள்ளீட்டு NAND வாயிலை உருவாக்குவோம்

NPN டிரான்சிஸ்டர்கள். லாஜிக் ஐ.சிக்கள் கிட்டத்தட்ட அதே வழியில் கட்டப்பட்டுள்ளன.

இரண்டு டிரான்சிஸ்டர் NAND கேட் திட்டவியல்:

வெளியீடு அதிகமாக இருந்தால் எல்.ஈ.டியை இணைக்க முடியும், எல்.ஈ.டி ஒளிரும் (எல்.ஈ.டி + வீ டெர்மினல் “ஒய்” இல் 330 ஓம் மின்தடையுடன் மற்றும் ஜிஎன்டிக்கு எதிர்மறையானது).

இரண்டு டிரான்சிஸ்டர்களின் அடிப்பகுதிக்கு நாம் உயர் சமிக்ஞையைப் பயன்படுத்தும்போது, இரண்டு டிரான்சிஸ்டர்களும் இயக்கப்படும், தரை சமிக்ஞை T1 இன் சேகரிப்பாளரிடம் கிடைக்கும், இதனால் வெளியீடு “LOW” ஆக மாறும்.

டிரான்சிஸ்டரில் ஏதேனும் ஒன்று முடக்கப்பட்டிருந்தால், அதாவது 'குறைந்த' சமிக்ஞையை அடித்தளத்திற்கு பயன்படுத்தினால், டி 1 சேகரிப்பாளரிடம் எந்த நில சமிக்ஞையும் கிடைக்காது, ஆனால் 1 கே புல் அப் மின்தடையின் காரணமாக நேர்மறை சமிக்ஞை வெளியீட்டில் கிடைக்கும் மற்றும் வெளியீடு திரும்பும் “உயர்”.

உங்கள் சொந்த தர்க்க NAND வாயிலை எவ்வாறு உருவாக்குவது என்பது இப்போது உங்களுக்குத் தெரியும்.

NAND வாயிலைப் பயன்படுத்தி பல்வேறு லாஜிக் வாயில்கள்:

NAND கேட் 'யுனிவர்சல் லாஜிக் கேட்' என்றும் அழைக்கப்படுகிறது, ஏனெனில் இந்த ஒற்றை வாயிலுடன் எந்த பூலியன் தர்க்கத்தையும் நாம் உருவாக்க முடியும். வெவ்வேறு தருக்க செயல்பாடுகளைக் கொண்ட ஐ.சி.க்களை உருவாக்குவதற்கும், ஒரு வாயிலைத் தயாரிப்பது பொருளாதாரத்திற்கும் ஒரு நன்மை.

மேலே உள்ள திட்டங்களில் 3 வகையான வாயில்கள் மட்டுமே காட்டப்பட்டுள்ளன, ஆனால், நாம் எந்த பூலியன் தர்க்கத்தையும் செய்யலாம்.

குவாட் நாண்ட் கேட் ஐசி 7400:

நீங்கள் சந்தையில் இருந்து ஒரு லாஜிக் NAND கேட்டை வாங்க விரும்பினால், மேலே உள்ள டிஐபி உள்ளமைவைப் பெறுவீர்கள்.

இது 14 ஊசிகளைக் கொண்டுள்ளது முள் # 7 மற்றும் முள் # 14 முறையே ஜிஎன்டி மற்றும் விசிசி. இது 5 வி இல் இயக்கப்படுகிறது.

பரப்புதல் தாமதம்:

பரப்புதல் தாமதம் என்பது வெளியீட்டை குறைந்த அளவிலிருந்து உயர்வாகவும், உள்ளீட்டைக் கொடுத்தபின் நேர்மாறாகவும் மாற்றுவதற்கான நேரமாகும்.

LOW முதல் HIGH வரை பரப்புதல் தாமதம் 22 நானோ விநாடிகள்.

HIGH முதல் LOW வரை பரப்புதல் தாமதம் 15 நானோ விநாடிகள்.

இன்னும் பல NAND கேட் ஐ.சி.க்கள் உள்ளன:

- 74LS00 குவாட் 2-உள்ளீடு

- 74LS10 டிரிபிள் 3-உள்ளீடு

- 74LS20 இரட்டை 4-உள்ளீடு

- 74LS30 ஒற்றை 8-உள்ளீடு

- CD4011 குவாட் 2-உள்ளீடு

- CD4023 டிரிபிள் 3-உள்ளீடு

- CD4012 இரட்டை 4-உள்ளீடு

NOR கேட் எவ்வாறு செயல்படுகிறது

இங்கே நாம் டிஜிட்டல் லாஜிக் NOR கேட் பற்றி ஆராயப்போகிறோம். அடிப்படை வரையறை, சின்னம், உண்மை அட்டவணை, மல்டி உள்ளீடு என்ஓஆர் கேட் ஆகியவற்றைப் பார்ப்போம், டிரான்சிஸ்டர் அடிப்படையிலான 2 உள்ளீட்டு என்ஓஆர் கேட், என்ஓஆர் கேட்டை மட்டுமே பயன்படுத்தி பல்வேறு லாஜிக் கேட்களை உருவாக்குவோம், இறுதியாக நாங்கள் என்ஓஆர் கேட் குறித்து ஒரு கண்ணோட்டத்தை எடுப்போம் ஐசி 7402.

லாஜிக் “NOR” கேட் என்றால் என்ன?

இது ஒரு மின்னணு வாயில் ஆகும், இதன் வெளியீடு “உயர்” அல்லது “1” அல்லது “உண்மை” ஆக மாறுகிறது அல்லது NOR வாயில்களின் அனைத்து உள்ளீடுகளும் “குறைந்த” அல்லது “0” அல்லது “பொய்” அல்லது “ எதிர்மறை சமிக்ஞை ”.

எடுத்துக்காட்டாக: ‘n’ எண்ணிக்கையிலான உள்ளீடுகளைக் கொண்ட ஒரு NOR வாயிலைச் சொல்லுங்கள், எல்லா உள்ளீடுகளும் “LOW” ஆக இருந்தால் வெளியீடு “HIGH” ஆக மாறும். ஒரு உள்ளீடு “உயர்” அல்லது “1” அல்லது “உண்மை” அல்லது “நேர்மறை சமிக்ஞை” என்றாலும், வெளியீடு “குறைந்த” அல்லது “0” அல்லது “பொய்” ஆக மாறும் அல்லது “எதிர்மறை சமிக்ஞையை” அளிக்கிறது.

குறிப்பு:

“உயர்”, “1”, “நேர்மறை சமிக்ஞை”, “உண்மை” என்ற சொல் அடிப்படையில் ஒரே மாதிரியானவை (நேர்மறை சமிக்ஞை என்பது பேட்டரி அல்லது மின்சாரம் வழங்கலின் நேர்மறை சமிக்ஞை).

“குறைந்த”, “0”, “எதிர்மறை சமிக்ஞை”, “பொய்” என்ற சொல் அடிப்படையில் ஒன்றே (எதிர்மறை சமிக்ஞை என்பது பேட்டரி அல்லது மின்சாரம் எதிர்மறை சமிக்ஞை).

லாஜிக் NOR கேட் சின்னத்தின் விளக்கம்:

இங்கே “A” மற்றும் “B” இரண்டு உள்ளீடுகள் மற்றும் “Y” வெளியீடு.

இந்த சின்னம் தலைகீழ் “ஓ” வாயிலாக “அல்லது” வாயில்.

தர்க்கம் “NOR” கேட் சமமான சுற்று:

லாஜிக் NOR கேட் என்பது லாஜிக் “OR” கேட் மற்றும் லாஜிக் “NOT” கேட் ஆகியவற்றின் கலவையாகும்.

தர்க்கம் NOR வாயிலுக்கான பூலியன் வெளிப்பாடு: ‘Y’ வெளியீடு ‘A’ மற்றும் ‘B’ ஆகிய இரண்டு உள்ளீடுகளின் நிரப்பு கூடுதலாகும். Y = ((A + B))

பூலியன் சேர்த்தல் (+) ஆல் குறிக்கப்படுகிறது மற்றும் நிரப்பு (தலைகீழ்) ஒரு கடிதத்தின் மீது ஒரு பட்டியில் (-) குறிக்கப்படுகிறது.

‘A’ என்பது ‘1’ மற்றும் ‘B’ என்பது ‘1’ என்றால் வெளியீடு ((A + B) ̅) = (1+ 1) ̅ = ‘0’ அல்லது “LOW”

‘A’ என்பது ‘0’ மற்றும் ‘B’ என்பது ‘1’ என்றால் வெளியீடு ((A + B) ̅) = (0+ 1) ̅ = ‘0’ அல்லது “LOW”

‘A’ என்பது ‘1’ மற்றும் ‘B’ என்பது ‘0’ என்றால் வெளியீடு ((A + B) ̅) = (1+ 0) ̅ = ‘0’ அல்லது “LOW”

‘A’ என்பது ‘0’ மற்றும் ‘B’ என்பது ‘0’ என்றால் வெளியீடு ((A + B) ̅) = (0+ 0) ̅ = ‘1’ அல்லது “HIGH”

மேற்கண்ட நிபந்தனைகள் உண்மை அட்டவணையில் எளிமைப்படுத்தப்பட்டுள்ளன.

உண்மை அட்டவணை (இரண்டு உள்ளீடு):

| ஒரு (உள்ளீடு) | பி (INPUT) | ஒய் (வெளியீடு) |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

3-உள்ளீடு “NOR” கேட்:

3 உள்ளீட்டு NOR வாயிலின் விளக்கம்:

லாஜிக் NOR வாயில்கள் ‘n’ எண்ணிக்கையிலான உள்ளீடுகளைக் கொண்டிருக்கலாம், அதாவது இது இரண்டுக்கும் மேற்பட்ட உள்ளீடுகளைக் கொண்டிருக்கலாம் (லாஜிக் NOR வாயில்களில் குறைந்தது இரண்டு உள்ளீடு மற்றும் எப்போதும் ஒரு வெளியீடு இருக்கும்).

3 உள்ளீட்டு NOR வாயிலுக்கு பூலியன் சமன்பாடு இப்படி மாறுகிறது: ((A + B + C) ̅) = Y, இதேபோல் 4 உள்ளீடு மற்றும் அதற்கு மேல்.

3 உள்ளீட்டு தர்க்கத்திற்கான உண்மை அட்டவணை NOR வாயில்:

| A (INPUT) | பி (INPUT) | சி (INPUT) | ஒய் (வெளியீடு) |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

பல உள்ளீட்டு தர்க்கம் NOR கேட்ஸ்:

வணிக ரீதியாக கிடைக்கக்கூடிய லாஜிக் NOR வாயில்கள் 2, 3 மற்றும் 4 உள்ளீடுகளில் மட்டுமே கிடைக்கின்றன. எங்களிடம் 4 க்கும் மேற்பட்ட உள்ளீடு இருந்தால், நாங்கள் வாயில்களை அடுக்க வேண்டும்.

எடுத்துக்காட்டாக, 5 இரண்டு உள்ளீட்டு NOR வாயில்களை பின்வருமாறு அடுக்கி நான்கு உள்ளீட்டு தர்க்க NOR வாயிலைக் கொண்டிருக்கலாம்:

இப்போது மேலே உள்ள சுற்றுக்கான பூலியன் சமன்பாடு Y = ((A + B + C + D) becomes ஆகிறது

இன்னும், குறிப்பிடப்பட்ட அனைத்து தருக்க விதிகளும் மேலே உள்ள சுற்றுக்கு பொருந்தும்.

மேலே உள்ள 4 உள்ளீடுகள் NOR வாயிலிலிருந்து 3 உள்ளீடுகளை மட்டுமே நீங்கள் பயன்படுத்தப் போகிறீர்கள் என்றால், ஒரு முள்-கீழே மின்தடையத்தை எந்த முள் ஒன்றிலும் இணைக்க முடியும், இப்போது அது 3 உள்ளீட்டு NOR வாயிலாக மாறும்.

டிரான்சிஸ்டர் அடிப்படையிலான இரண்டு உள்ளீடு லாஜிக் NOR கேட்:

இப்போது எங்களுக்குத் தெரியும், ஒரு தர்க்கம் NOR கேட் எவ்வாறு செயல்படுகிறது, இரண்டு NPN டிரான்சிஸ்டர்களைப் பயன்படுத்தி 2 உள்ளீட்டு NOR வாயிலை உருவாக்குவோம். லாஜிக் ஐ.சிக்கள் கிட்டத்தட்ட அதே வழியில் கட்டப்பட்டுள்ளன.

இரண்டு டிரான்சிஸ்டர் NOR கேட் திட்டவியல்:

வெளியீடு அதிகமாக இருந்தால் எல்.ஈ.டியை இணைக்க முடியும், எல்.ஈ.டி ஒளிரும் (எல்.ஈ.டி + வீ டெர்மினல் “ஒய்” இல் 330 ஓம் மின்தடையுடன் மற்றும் ஜிஎன்டிக்கு எதிர்மறையானது).

இரண்டு டிரான்சிஸ்டர்களின் அடிப்பகுதிக்கு “உயர்” சமிக்ஞையைப் பயன்படுத்தும்போது, இரண்டு டிரான்சிஸ்டர்களும் இயங்கும் மற்றும் தரை சமிக்ஞை T1 மற்றும் T2 சேகரிப்பாளரிடம் கிடைக்கும், இதனால் வெளியீடு “LOW” ஆக மாறும்.

டிரான்சிஸ்டரில் ஏதேனும் ஒன்றுக்கு “ஹை” பயன்படுத்தினால், வெளியீட்டில் எதிர்மறை சமிக்ஞை கிடைக்கும், இதனால் வெளியீடு “குறைந்த” போகும்.

இரண்டு டிரான்சிஸ்டர்களின் அடிப்பகுதிக்கு “குறைந்த” சமிக்ஞையைப் பயன்படுத்தினால், இரண்டும் முடக்கப்படும், ஆனால் இழுக்கும்-மின்தடையின் காரணமாக வெளியீடு “உயர்” ஆக மாறும்.

உங்கள் சொந்த தர்க்க NOR வாயிலை எவ்வாறு உருவாக்குவது என்பது இப்போது உங்களுக்குத் தெரியும்.

NOR வாயிலைப் பயன்படுத்தி பல்வேறு லாஜிக் வாயில்கள்:

குறிப்பு: NAND மற்றும் NOR ஆகியவை இரண்டு வாயில்கள், இல்லையெனில் உலகளாவிய வாயில்கள் என்று அழைக்கப்படுகின்றன.

NOR வாயில் ஒரு 'உலகளாவிய தர்க்க வாயில்' ஆகும், ஏனெனில் இந்த ஒற்றை வாயில் மூலம் எந்த பூலியன் தர்க்கங்களையும் நாம் உருவாக்க முடியும். வெவ்வேறு தருக்க செயல்பாடுகளைக் கொண்ட ஐ.சி.க்களை உருவாக்குவதற்கும், ஒரு வாயிலைத் தயாரிப்பது சிக்கனமானது என்பதற்கும் இது ஒரு நன்மை, இது NAND வாயிலுக்கும் சமம்.

மேலே உள்ள திட்டங்களில் 3 வகையான வாயில்கள் மட்டுமே காண்பிக்கப்படுகின்றன, ஆனால், நாங்கள் எந்த பூலியன் தர்க்கங்களையும் செய்யலாம்.

குவாட் NOR கேட் ஐசி 7402:

நீங்கள் சந்தையில் இருந்து ஒரு லாஜிக் NOR கேட்டை வாங்க விரும்பினால், மேலே உள்ள டிஐபி உள்ளமைவைப் பெறுவீர்கள்.

இது 14 ஊசிகளைக் கொண்டுள்ளது முள் # 7 மற்றும் முள் # 14 முறையே ஜிஎன்டி மற்றும் விசிசி. இது 5 வி இல் இயக்கப்படுகிறது.

பரப்புதல் தாமதம்:

பரப்புதல் தாமதம் என்பது வெளியீட்டை குறைந்த அளவிலிருந்து உயர்வாகவும், உள்ளீட்டைக் கொடுத்தபின் நேர்மாறாகவும் மாற்றுவதற்கான நேரமாகும்.

LOW முதல் HIGH வரை பரப்புதல் தாமதம் 22 நானோ விநாடிகள்.

HIGH முதல் LOW வரை பரப்புதல் தாமதம் 15 நானோ விநாடிகள்.

இன்னும் பல NOR கேட் ஐ.சி.க்கள் உள்ளன:

- 74LS02 குவாட் 2-உள்ளீடு

- 74LS27 டிரிபிள் 3-உள்ளீடு

- 74LS260 இரட்டை 4-உள்ளீடு

- CD4001 குவாட் 2-உள்ளீடு

- CD4025 டிரிபிள் 3-உள்ளீடு

- CD4002 இரட்டை 4-உள்ளீடு

லாஜிக் நோட் கேட்

இந்த இடுகையில் தர்க்கம் “NOT” வாயில் பற்றி ஆராயப்போகிறோம். அதன் அடிப்படை வரையறை, சின்னம், உண்மை அட்டவணை, NAND மற்றும் NOR கேட் சமமானவர்கள், ஷ்மிட் இன்வெர்ட்டர்கள், ஷ்மிட் நோட் கேட் ஆஸிலேட்டர், டிரான்சிஸ்டரைப் பயன்படுத்தி கேட் இல்லை, இறுதியாக லாஜிக் NOT கேட் இன்வெர்ட்டர் ஐசி 7404 ஐப் பார்ப்போம்.

டிஜிட்டல் இன்வெர்ட்டர் என்றும் அழைக்கப்படும் லாஜிக் நோட் கேட் விவரங்களை நாம் ஆராயத் தொடங்குவதற்கு முன், வீடு அல்லது அலுவலகத்தில் சூரிய அல்லது காப்பு மின்சாரம் வழங்குவதில் பயன்படுத்தப்படும் “பவர் இன்வெர்ட்டர்களுடன்” ஒருவர் குழப்பமடையக்கூடாது.

லாஜிக் “NOT” கேட் என்றால் என்ன?

இது ஒரு ஒற்றை உள்ளீடு மற்றும் ஒற்றை வெளியீட்டு தர்க்க வாயில் ஆகும், இதன் வெளியீடு உள்ளீட்டுக்கு பூர்த்தி ஆகும்.

மேலே உள்ள வரையறை, உள்ளீடு “உயர்” அல்லது “1” அல்லது “உண்மை” அல்லது “நேர்மறை சமிக்ஞை” என்றால் வெளியீடு “குறைந்த” அல்லது “0” அல்லது “தவறான” அல்லது “எதிர்மறை சமிக்ஞை” ஆக இருக்கும்.

உள்ளீடு “குறைந்த” அல்லது “0” அல்லது “தவறான” அல்லது “எதிர்மறை சமிக்ஞை” என்றால் வெளியீடு “உயர்” அல்லது “1” அல்லது “உண்மை” அல்லது “நேர்மறை சமிக்ஞை”

குறிப்பு:

“உயர்”, “1”, “நேர்மறை சமிக்ஞை”, “உண்மை” என்ற சொல் அடிப்படையில் ஒரே மாதிரியானவை (நேர்மறை சமிக்ஞை என்பது பேட்டரி அல்லது மின்சாரம் வழங்கலின் நேர்மறை சமிக்ஞை).

“குறைந்த”, “0”, “எதிர்மறை சமிக்ஞை”, “பொய்” என்ற சொல் அடிப்படையில் ஒன்றே (எதிர்மறை சமிக்ஞை என்பது பேட்டரி அல்லது மின்சாரம் எதிர்மறை சமிக்ஞை).

லாஜிக் நோட் கேட் விளக்கம்:

“A” என்பது உள்ளீடு என்றும் “Y” வெளியீடு என்றும் வைத்துக் கொள்வோம், லாஜிக் NOT வாயிலுக்கான பூலியன் சமன்பாடு: Ā = Y.

வெளியீடு உள்ளீட்டின் தலைகீழ் என்று சமன்பாடு கூறுகிறது.

தர்க்கம் NOT வாயிலுக்கான உண்மை அட்டவணை:

| TO (INPUT) | ஒய் (வெளியீடு) |

| 0 | 1 |

| 1 | 0 |

வாயில்கள் எப்போதும் ஒற்றை உள்ளீட்டைக் கொண்டிருக்கும் (எப்போதும் ஒற்றை வெளியீட்டைக் கொண்டிருக்கும்) இது முடிவெடுக்கும் சாதனங்களாக வகைப்படுத்தப்படுகிறது. முக்கோணத்தின் நுனியில் உள்ள “ஓ” சின்னம் பூர்த்தி அல்லது தலைகீழ் என்பதைக் குறிக்கிறது.

இந்த “ஓ” சின்னம் தர்க்கம் “NOT” வாயிலுக்கு மட்டுமல்ல, எந்தவொரு தர்க்க வாயில்களாலும் அல்லது எந்த டிஜிட்டல் சுற்றுகளாலும் பயன்படுத்தப்படலாம். “O” உள்ளீட்டில் இருந்தால், உள்ளீடு செயலில்-குறைவாக இருப்பதாக இது கூறுகிறது.

செயலில்-குறைந்த: “குறைந்த” உள்ளீடு வழங்கப்படும் போது வெளியீடு செயலில் மாறும் (டிரான்சிஸ்டர், எல்இடி அல்லது ரிலே போன்றவற்றை செயல்படுத்துகிறது).

NAND மற்றும் NOR கேட்ஸ் சமமானவை:

அனைத்து உள்ளீட்டு ஊசிகளையும் இணைப்பதன் மூலம் தர்க்கம் “NAND” மற்றும் தர்க்க “NOR” வாயில்களைப் பயன்படுத்தி “NOT” வாயிலை உருவாக்க முடியும், இது 3, 4 மற்றும் அதிக உள்ளீட்டு ஊசிகளைக் கொண்ட வாயில்களுக்கு பொருந்தும்.

டிரான்சிஸ்டர் அடிப்படையிலான லாஜிக் “NOT” கேட்:

“NOT” என்ற தர்க்கத்தை ஒரு NPN டிரான்சிஸ்டர் மற்றும் 1K மின்தடையால் உருவாக்க முடியும். டிரான்சிஸ்டரின் அடிப்பகுதிக்கு “உயர்” சமிக்ஞையைப் பயன்படுத்தினால், தரையானது டிரான்சிஸ்டரின் சேகரிப்பாளருடன் இணைக்கப்படும், இதனால் வெளியீடு “குறைந்த” ஆக மாறும்.

டிரான்சிஸ்டரின் அடிப்பகுதிக்கு “குறைந்த” சமிக்ஞையைப் பயன்படுத்தினால், டிரான்சிஸ்டர் முடக்கத்தில் உள்ளது, அது தரையில் இணைக்கப்படாது, ஆனால், வெளியீடு “உயர்” இழுக்கப்படுவதால் வி.சி.சி உடன் இணைக்கப்படும். இதனால் டிரான்சிஸ்டரைப் பயன்படுத்தி ஒரு தர்க்க “NOT” வாயிலை உருவாக்க முடியும்.

ஷ்மிட் இன்வெர்ட்டர்ஸ்:

ஷ்மிட் இன்வெர்ட்டர்களின் பயன்பாடு மற்றும் செயல்பாட்டை விளக்க இந்த கருத்தை ஒரு தானியங்கி பேட்டரி சார்ஜர் மூலம் ஆராய்வோம். லி-அயன் பேட்டரி சார்ஜிங் நடைமுறையின் உதாரணத்தை எடுத்துக் கொள்வோம்.

பேட்டரி 3 V முதல் 3.2 V ஐ தாக்கும் போது 3.7 V லி-அயன் பேட்டரி சார்ஜ் செய்யப்படுகிறது, சார்ஜ் செய்யும் போது பேட்டரி மின்னழுத்தம் படிப்படியாக உயரும் மற்றும் பேட்டரி 4.2 V இல் துண்டிக்கப்பட வேண்டும். சார்ஜ் செய்த பிறகு, பேட்டரியின் திறந்த சுற்று மின்னழுத்தம் 4.0 V ஐ சுற்றி குறைகிறது .

ஒரு மின்னழுத்த சென்சார் கட்-ஆஃப் வரம்பை அளவிடும் மற்றும் சார்ஜ் செய்வதை நிறுத்த ரிலேவைத் தூண்டுகிறது. ஆனால் மின்னழுத்தம் 4.2V க்குக் கீழே குறையும் போது, சார்ஜர் சார்ஜ் செய்யப்படாததைக் கண்டறிந்து, 4.2V மற்றும் கட்-ஆஃப் வரை சார்ஜ் தொடங்கும் போது, மீண்டும் பேட்டரி மின்னழுத்தம் 4.0V க்கு விழுந்து மீண்டும் கட்டணத்தைத் தொடங்குகிறது, மேலும் இந்த பைத்தியம் சுழற்சிகள் மீண்டும் மீண்டும் வரும்.

இது பேட்டரியை விரைவாகக் கொல்லும், இந்த சிக்கலை சமாளிக்க எங்களுக்கு குறைந்த வாசல் நிலை அல்லது “எல்டிவி” தேவைப்படுகிறது, இதனால் பேட்டரி 3 வி முதல் 3.2 வி வரை விழும் வரை பேட்டரி சார்ஜ் செய்யாது. மேல் வாசல் மின்னழுத்தம் அல்லது “யுடிவி” இந்த எடுத்துக்காட்டில் 4.2 வி.

மின்னழுத்தம் மேல் வாசல் மின்னழுத்தத்தைக் கடக்கும்போது அதன் வெளியீட்டு நிலையை மாற்ற ஒரு ஷ்மிட் இன்வெர்ட்டர் செய்யப்படுகிறது, மேலும் உள்ளீடு குறைந்த வாசல் மின்னழுத்தத்தை அடையும் வரை அது அப்படியே இருக்கும்.

இதேபோல், உள்ளீடு குறைந்த வாசல் மின்னழுத்தத்தைக் கடந்ததும், உள்ளீடு மேல் வாசல் மின்னழுத்தத்தை அடையும் வரை வெளியீடு அப்படியே இருக்கும்.

எல்டிவி மற்றும் யுடிவிக்கு இடையில் இது அதன் நிலையை மாற்றாது.

இப்போது, இதன் காரணமாக, ஆன் / ஆஃப் மிகவும் மென்மையாக இருக்கும் மற்றும் தேவையற்ற ஊசலாட்டம் அகற்றப்படும், மேலும் மின்சுற்றுக்கு மின்சுற்று எதிர்ப்பு அதிகமாக இருக்கும்.

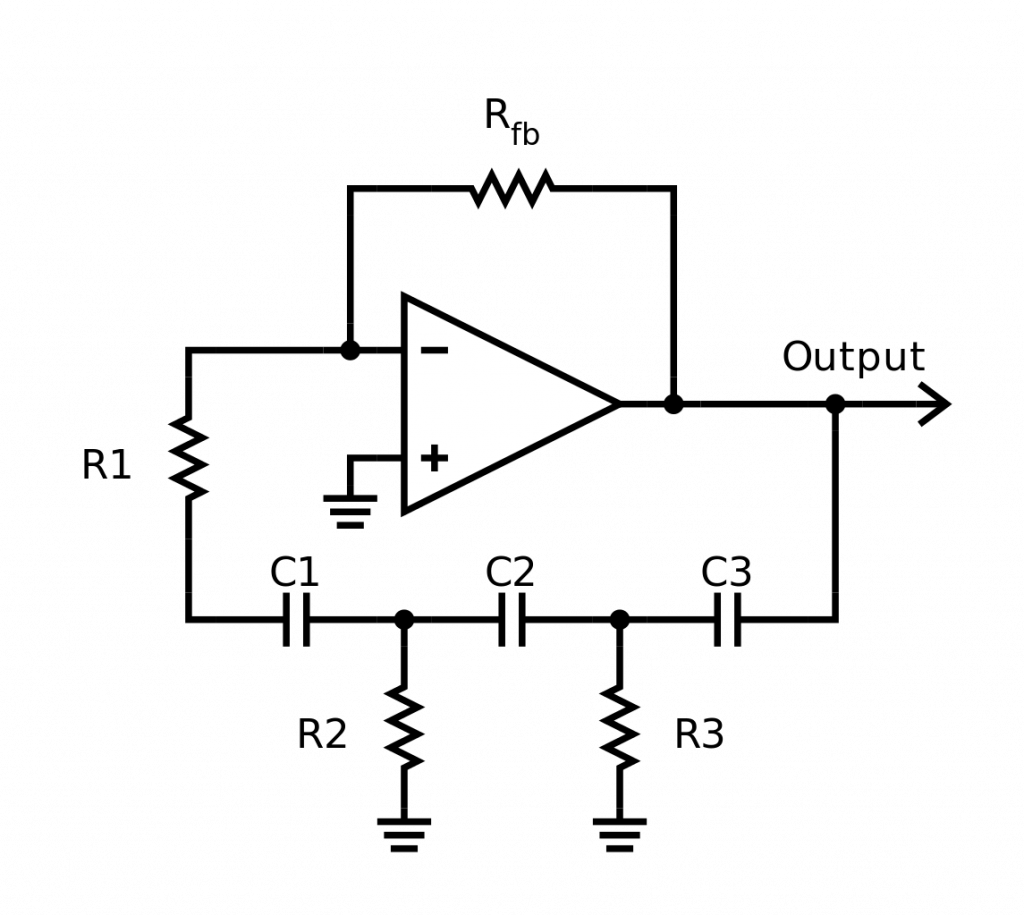

ஷ்மிட் நோட் கேட் ஆஸிலேட்டர்:

மேலே உள்ள சுற்று 33% கடமை சுழற்சியில் சதுர அலையை உருவாக்கும் ஒரு ஆஸிலேட்டர் ஆகும். ஆரம்பத்தில் மின்தேக்கி வெளியேற்றப்பட்ட நிலையில் உள்ளது மற்றும் NOT வாயிலின் உள்ளீட்டில் தரை சமிக்ஞை கிடைக்கும்.

வெளியீடு நேர்மறையாக மாறி மின்தேக்கியை மின்தடையம் “ஆர்” வழியாக சார்ஜ் செய்கிறது, இன்வெர்ட்டரின் மேல் வாசல் மின்னழுத்தம் வரை மின்தேக்கி கட்டணம் வசூலிக்கிறது மற்றும் நிலையை மாற்றுகிறது, வெளியீடு எதிர்மறை சமிக்ஞையாக மாறும் மற்றும் மின்தேக்கி மின்தேக்கி மின்னழுத்தத்தை அடையும் வரை மின்தேக்கி “ஆர்” வழியாக வெளியேற்றத் தொடங்குகிறது. குறைந்த வாசல் நிலை மற்றும் நிலையை மாற்றுகிறது, வெளியீடு நேர்மறையாக மாறி மின்தேக்கியை சார்ஜ் செய்கிறது.

மின்சுற்று சுற்றுக்கு வழங்கப்படும் வரை இந்த சுழற்சி மீண்டும் நிகழ்கிறது.

மேலே உள்ள ஆஸிலேட்டரின் அதிர்வெண்ணைக் கணக்கிடலாம்: F = 680 / RC

எங்கே, எஃப் அதிர்வெண்.

ஆர் என்பது ஓம்ஸில் எதிர்ப்பு.

சி என்பது ஃபாராட்டில் கொள்ளளவு.

சதுர அலை மாற்றி:

மேலே உள்ள சுற்று சைன் அலை சமிக்ஞையை சதுர அலைக்கு மாற்றும், உண்மையில் இது எந்த அனலாக் அலைகளையும் சதுர அலைகளாக மாற்றும்.

இரண்டு மின்தடையங்கள் R1 மற்றும் R2 மின்னழுத்த வகுப்பியாக செயல்படுகின்றன, இது ஒரு சார்பு புள்ளியைப் பெற பயன்படுத்தப்படுகிறது மற்றும் மின்தேக்கி எந்த DC சமிக்ஞைகளையும் தடுக்கிறது.

உள்ளீட்டு சமிக்ஞை மேல் வாசல் மட்டத்திற்கு மேலே அல்லது குறைந்த வாசல் மட்டத்திற்கு கீழே சென்றால் வெளியீடு மாறும்

சமிக்ஞையின் படி குறைந்த அல்லது உயர், இது சதுர அலையை உருவாக்குகிறது.

ஐசி 7404 நோட் கேட் இன்வெர்ட்டர்:

ஐசி 7404 என்பது பொதுவாகப் பயன்படுத்தப்படும் லாஜிக் NOT கேட் ஐசி. இது 14 ஊசிகளைக் கொண்டுள்ளது, முள் # 7 தரையில் உள்ளது மற்றும் முள் # 14 வி.சி.சி. இயக்க மின்னழுத்தம் 4.5 வி முதல் 5 வி வரை இருக்கும்.

பரப்புதல் தாமதம்:

பரவல் தாமதம் என்பது ஒரு உள்ளீட்டைக் கொடுத்த பிறகு வெளியீட்டைச் செயலாக்க வாயில் எடுக்கும் நேரம்.

தர்க்கத்தில் “NOT” கேட் அதன் நிலையை உயர்விலிருந்து குறைந்ததாக மாற்ற 22 நானோ வினாடிகள் ஆகும்.

இன்னும் பல தர்க்கங்கள் உள்ளன “நோட் கேட் ஐசிக்கள்:

L 74LS04 ஹெக்ஸ் இன்வெர்டிங் நோட் கேட்

L 74LS14 ஹெக்ஸ் ஷ்மிட் இன்வெர்டிங் நாட் கேட்

L 74LS1004 ஹெக்ஸ் இன்வெர்டிங் டிரைவர்கள்

• CD4009 ஹெக்ஸ் இன்வெர்டிங் நாட் கேட்

40 சிடி 4069 ஹெக்ஸ் இன்வெர்டிங் நாட் கேட்

அல்லது வாயில் எவ்வாறு இயங்குகிறது

இப்போது டிஜிட்டல் லாஜிக் அல்லது கேட்ஸ் பற்றி ஆராய்வோம். அடிப்படை வரையறை, சின்னம், உண்மை அட்டவணை, மல்டி உள்ளீடு அல்லது வாயில் ஆகியவற்றைப் பார்ப்போம், டிரான்சிஸ்டர் அடிப்படையிலான 2 உள்ளீடு அல்லது வாயிலை உருவாக்குவோம், இறுதியாக OR வாயில் ஐசி 7432 குறித்து ஒரு கண்ணோட்டத்தை எடுப்போம்.

லாஜிக் “அல்லது” கேட் என்றால் என்ன?

இது ஒரு மின்னணு வாயில் ஆகும், அதன் வெளியீடு “குறைந்த” அல்லது “0” அல்லது “பொய்” ஆக மாறும் அல்லது OR வாயில்களின் அனைத்து உள்ளீடுகளும் “குறைந்த” அல்லது “0” அல்லது “பொய்” அல்லது “ எதிர்மறை சமிக்ஞை ”.

எடுத்துக்காட்டாக: அனைத்து உள்ளீடுகளும் “LOW” ஆக இருந்தால், ‘n’ உள்ளீடுகளின் எண்ணிக்கையுடன் OR வாயில் சொல்லுங்கள். வெளியீடு “LOW” ஆக மாறும். ஒரு உள்ளீடு “உயர்” அல்லது “1” அல்லது “உண்மை” அல்லது “நேர்மறை சமிக்ஞை” என்றாலும், வெளியீடு “உயர்” அல்லது “1” அல்லது “உண்மை” ஆக மாறுகிறது அல்லது “நேர்மறை சமிக்ஞையை” அளிக்கிறது.

குறிப்பு:

“உயர்”, “1”, “நேர்மறை சமிக்ஞை”, “உண்மை” என்ற சொல் அடிப்படையில் ஒரே மாதிரியானவை (நேர்மறை சமிக்ஞை என்பது பேட்டரி அல்லது மின்சாரம் வழங்கலின் நேர்மறை சமிக்ஞை).

“குறைந்த”, “0”, “எதிர்மறை சமிக்ஞை”, “பொய்” என்ற சொல் அடிப்படையில் ஒன்றே (எதிர்மறை சமிக்ஞை என்பது பேட்டரி அல்லது மின்சாரம் எதிர்மறை சமிக்ஞை).

லாஜிக் அல்லது கேட் சின்னத்தின் விளக்கம்:

இங்கே “A” மற்றும் “B” இரண்டு உள்ளீடுகள் மற்றும் “Y” வெளியீடு.

தர்க்கம் அல்லது வாயிலுக்கான பூலியன் வெளிப்பாடு: வெளியீடு ‘Y’ என்பது ‘A’ மற்றும் ‘B’, (A + B) = Y ஆகிய இரண்டு உள்ளீடுகளின் கூடுதலாகும்.

பூலியன் சேர்த்தல் (+) ஆல் குறிக்கப்படுகிறது

‘A’ என்பது ‘1’ மற்றும் ‘B’ என்பது ‘1’ என்றால் வெளியீடு (A + B) = 1 + 1 = ‘1’ அல்லது “high”

‘A’ என்பது ‘0’ மற்றும் ‘B’ ‘1’ என்றால் வெளியீடு (A + B) = 0 + 1 = ‘1’ அல்லது “high”

‘A’ என்பது ‘1’ மற்றும் ‘B’ என்பது ‘0’ என்றால் வெளியீடு (A + B) = 1 + 0 = ‘1’ அல்லது “high”

‘A’ என்பது ‘0’ மற்றும் ‘B’ என்பது ‘0’ என்றால் வெளியீடு (A + B) = 0 + 0 = ‘0’ அல்லது “Low”

மேற்கண்ட நிபந்தனைகள் உண்மை அட்டவணையில் எளிமைப்படுத்தப்பட்டுள்ளன.

உண்மை அட்டவணை (இரண்டு உள்ளீடு):

| ஒரு (உள்ளீடு) | பி (INPUT) | ஒய் (வெளியீடு) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

3-உள்ளீடு “அல்லது” கேட்:

3 உள்ளீடு அல்லது வாயிலின் விளக்கம்:

தர்க்கம் அல்லது வாயில்கள் ‘n’ எண்ணிக்கையிலான உள்ளீடுகளைக் கொண்டிருக்கலாம், அதாவது இது இரண்டுக்கும் மேற்பட்ட உள்ளீடுகளைக் கொண்டிருக்கலாம் (லாஜிக் அல்லது வாயில்களில் குறைந்தது இரண்டு உள்ளீடு மற்றும் எப்போதும் ஒரு வெளியீடு இருக்கும்).

3 உள்ளீட்டு தர்க்கம் அல்லது வாயிலுக்கு பூலியன் சமன்பாடு இப்படி மாறுகிறது: (A + B + C) = Y, இதேபோல் 4 உள்ளீடு மற்றும் அதற்கு மேல்.

3 உள்ளீட்டு தர்க்கம் அல்லது வாயிலுக்கான உண்மை அட்டவணை:

| A (INPUT) | பி (INPUT) | சி (INPUT) | ஒய் (வெளியீடு) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |

பல உள்ளீட்டு தர்க்கம் அல்லது வாயில்கள்:

வணிக ரீதியாக கிடைக்கக்கூடிய லாஜிக் அல்லது வாயில்கள் 2, 3 மற்றும் 4 உள்ளீடுகளில் மட்டுமே கிடைக்கின்றன. எங்களிடம் 4 க்கும் மேற்பட்ட உள்ளீடு இருந்தால், நாங்கள் வாயில்களை அடுக்க வேண்டும்.

2 உள்ளீடு அல்லது வாயில்களை பின்வருமாறு அடுக்கி வைப்பதன் மூலம் ஆறு உள்ளீட்டு தர்க்கம் அல்லது வாயிலை நாம் கொண்டிருக்கலாம்:

இப்போது மேலே உள்ள சுற்றுக்கான பூலியன் சமன்பாடு Y = (A + B) + (C + D) + (E + F) ஆகிறது

இன்னும், குறிப்பிடப்பட்ட அனைத்து தருக்க விதிகளும் மேலே உள்ள சுற்றுக்கு பொருந்தும்.

மேலே உள்ள 6 உள்ளீடுகள் அல்லது வாயிலிலிருந்து 5 உள்ளீடுகளை மட்டுமே நீங்கள் பயன்படுத்தப் போகிறீர்கள் என்றால், எந்த ஒரு முனையிலும் ஒரு இழுக்கும்-கீழே மின்தடையத்தை நாங்கள் இணைக்க முடியும், இப்போது அது 5 உள்ளீடு அல்லது வாயிலாக மாறுகிறது.

டிரான்சிஸ்டர் அடிப்படையிலான இரண்டு உள்ளீடு லாஜிக் அல்லது கேட்:

இப்போது எங்களுக்குத் தெரியும், ஒரு தர்க்கம் அல்லது வாயில் எவ்வாறு செயல்படுகிறது, இரண்டு NPN டிரான்சிஸ்டர்களைப் பயன்படுத்தி 2 உள்ளீடு அல்லது வாயிலை உருவாக்குவோம். லாஜிக் ஐ.சிக்கள் கிட்டத்தட்ட அதே வழியில் கட்டப்பட்டுள்ளன.

இரண்டு டிரான்சிஸ்டர் அல்லது கேட் திட்டவியல்:

“Y” வெளியீட்டில் எல்.ஈ.டி அதிகமாக இருந்தால் எல்.ஈ.டி ஒளிரும் (எல்.ஈ.டி + வீ டெர்மினல் “ஒய்” இல் 330 ஓம் மின்தடையுடன் மற்றும் ஜிஎன்டிக்கு எதிர்மறையானது).

இரண்டு டிரான்சிஸ்டர்களின் அடிப்பகுதிக்கு நாம் குறைந்த சமிக்ஞையைப் பயன்படுத்தும்போது, இரண்டு டிரான்சிஸ்டர்களும் முடக்கப்படும், தரை சமிக்ஞை T2 / T1 இன் உமிழ்ப்பில் 1k புல்-டவுன் மின்தடை வழியாக கிடைக்கும், இதனால் வெளியீடு குறைவாக மாறும்.

டிரான்சிஸ்டரில் ஏதேனும் ஒன்று இயக்கத்தில் இருந்தால், நேர்மறை மின்னழுத்தம் T2 / T1 இன் உமிழ்ப்பில் கிடைக்கும், இதனால் வெளியீடு HIGH ஆக மாறும்.

உங்கள் சொந்த தர்க்கம் அல்லது வாயிலை எவ்வாறு உருவாக்குவது என்பது இப்போது உங்களுக்குத் தெரியும்.

குவாட் அல்லது கேட் ஐசி 7432:

நீங்கள் சந்தையில் இருந்து லாஜிக் அல்லது கேட்டை வாங்க விரும்பினால், மேலே உள்ளமைவில் நீங்கள் பெறுவீர்கள்.

இது 14 ஊசிகளைக் கொண்டுள்ளது முள் # 7 மற்றும் முள் # 14 முறையே ஜிஎன்டி மற்றும் விசிசி. இது 5 வி இல் இயக்கப்படுகிறது.

பரப்புதல் தாமதம்:

பரப்புதல் தாமதம் என்பது வெளியீடு குறைந்த அளவிலிருந்து உயர் மற்றும் அதற்கு நேர்மாறாக மாறுவதற்கு எடுக்கப்பட்ட நேரம்.

LOW முதல் HIGH வரை பரப்புதல் தாமதம் 25 டிகிரி செல்சியஸில் 7.4 நானோ விநாடிகள் ஆகும்.

HIGH முதல் LOW வரை பரப்புதல் தாமதம் 25 டிகிரி செல்சியஸில் 7.7 நானோ விநாடிகள் ஆகும்.

L 74LS32 குவாட் 2-உள்ளீடு

40 CD4071 குவாட் 2-உள்ளீடு

40 CD4075 டிரிபிள் 3-உள்ளீடு

40 CD4072 இரட்டை 4-உள்ளீடு

லாஜிக் பிரத்தியேக –ஓ கேட்

இந்த இடுகையில் நாம் லாஜிக் XOR கேட் அல்லது பிரத்தியேக- OR கேட் பற்றி ஆராயப்போகிறோம். அடிப்படை வரையறை, சின்னம், உண்மை அட்டவணை, XOR சமமான சுற்று, தர்க்க NAND வாயில்களைப் பயன்படுத்தி XOR உணர்தல் ஆகியவற்றைப் பார்ப்போம், இறுதியாக, குவாட் 2 உள்ளீடு Ex-OR கேட் IC 7486 பற்றிய கண்ணோட்டத்தை நாங்கள் எடுப்போம்.

முந்தைய இடுகைகளில், “AND”, “OR” மற்றும் “NOT” ஆகிய மூன்று அடிப்படை தர்க்க வாயில்களைப் பற்றி அறிந்து கொண்டோம். இந்த மூன்று அடிப்படை வாயில்களைப் பயன்படுத்தி “NAND” மற்றும் “NOR” ஆகிய இரண்டு புதிய தர்க்க வாயில்களை உருவாக்க முடியும் என்பதையும் நாங்கள் அறிந்தோம்.

இன்னும் இரண்டு தர்க்க வாயில்கள் உள்ளன, ஆனால் இவை இரண்டும் அடிப்படை வாயில்கள் அல்ல, ஆனால் இது மற்ற தர்க்க வாயில்களின் கலவையால் கட்டப்பட்டுள்ளது மற்றும் அதன் பூலியன் சமன்பாடு மிகவும் முக்கியமானது மற்றும் மிகவும் பயனுள்ளதாக இருக்கிறது, இது தனித்துவமான தர்க்க வாயில்களாக கருதப்படுகிறது.

இந்த இரண்டு தர்க்க வாயில்களும் “பிரத்தியேக OR” வாயில் மற்றும் “பிரத்யேக NOR” ஆகும். இந்த இடுகையில் நாம் தர்க்கம் பிரத்தியேக அல்லது வாயில் பற்றி மட்டுமே ஆராயப்போகிறோம்.

“பிரத்யேக அல்லது” வாயில் என்றால் என்ன?

இது ஒரு எலக்ட்ரானிக் கேட் ஆகும், அதன் வெளியீடு “உயர்” அல்லது “1” அல்லது “உண்மை” ஆக மாறுகிறது அல்லது இரண்டு தர்க்க உள்ளீடுகளும் ஒருவருக்கொருவர் வேறுபடும்போது “நேர்மறை சமிக்ஞையை” அளிக்கிறது (இது இரண்டு 2 உள்ளீட்டு எக்ஸ் மட்டுமே பொருந்தும் -ஓ கேட்).

எடுத்துக்காட்டாக: 'இரண்டு' உள்ளீடுகளுடன் ஒரு பிரத்யேக அல்லது வாயிலைச் சொல்லுங்கள், உள்ளீட்டு முள் A ஒன்று 'உயர்' மற்றும் உள்ளீட்டு முள் B 'குறைந்த' எனில், வெளியீடு 'உயர்' அல்லது '1' அல்லது 'உண்மை' அல்லது “நேர்மறை சமிக்ஞை”.

இரண்டு உள்ளீடுகளும் ஒரே தர்க்க நிலை என்றால், அதாவது இரண்டு ஊசிகளும் “உயர்” அல்லது இரண்டு ஊசிகளும் “குறைந்த” வெளியீடு “குறைந்த” அல்லது “0” அல்லது “தவறான” அல்லது “எதிர்மறை சமிக்ஞை” ஆக மாறும்.

குறிப்பு:

“உயர்”, “1”, “நேர்மறை சமிக்ஞை”, “உண்மை” என்ற சொல் அடிப்படையில் ஒரே மாதிரியானவை (நேர்மறை சமிக்ஞை என்பது பேட்டரி அல்லது மின்சாரம் வழங்கலின் நேர்மறை சமிக்ஞை).

“குறைந்த”, “0”, “எதிர்மறை சமிக்ஞை”, “பொய்” என்ற சொல் அடிப்படையில் ஒன்றே (எதிர்மறை சமிக்ஞை என்பது பேட்டரி அல்லது மின்சாரம் எதிர்மறை சமிக்ஞை).

லாஜிக் பிரத்தியேக அல்லது வாயிலின் விளக்கம்:

இங்கே “A” மற்றும் “B” இரண்டு உள்ளீடுகள் மற்றும் “Y” வெளியீடு.

தர்க்கத்திற்கான பூலியன் வெளிப்பாடு Ex-OR வாயில்: Y = (A.) ̅B + A.B

‘A’ என்பது ‘1’ மற்றும் ‘B’ என்பது ‘1’ என்றால் வெளியீடு (A ̅.B + A.B ̅) = 0 x 1 + 1 x 0 = ‘1’ அல்லது “LOW”

‘A’ என்பது ‘0’ மற்றும் ‘B’ என்பது ‘1’ என்றால் வெளியீடு (A ̅.B + A.B ̅) = 1 x 1 + 0 x 0 = ‘1’ அல்லது “HIGH”

‘A’ என்பது ‘1’ மற்றும் ‘B’ என்பது ‘0’ என்றால் வெளியீடு (A ̅.B + A.B ̅) = 0 x 0 + 1 x 1 = ‘1’ அல்லது “HIGH”

‘A’ என்பது ‘0’ மற்றும் ‘B’ என்பது ‘0’ என்றால் வெளியீடு (A ̅.B + A.B ̅) = 1 x 0 + 0 x 1 = ‘0’ அல்லது “Low”

மேற்கண்ட நிபந்தனைகள் உண்மை அட்டவணையில் எளிமைப்படுத்தப்பட்டுள்ளன.

உண்மை அட்டவணை (இரண்டு உள்ளீடு):

| ஒரு (உள்ளீடு) | பி (INPUT) | ஒய் (வெளியீடு) |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

மேலே உள்ள இரண்டு உள்ளீட்டு தர்க்கத்தில் Ex-OR வாயில், இரண்டு உள்ளீடுகள் வேறுபட்டால், அதாவது “1” மற்றும் “0” வெளியீடு “HIGH” ஆக மாறும். ஆனால் 3 அல்லது அதற்கு மேற்பட்ட உள்ளீட்டு தர்க்கம் Ex-OR அல்லது பொதுவாக Ex-OR இன் வெளியீடு “HIGH” ஆக மாறும், ODD எண் தர்க்கத்தின் “HIGH” வாயிலுக்கு பயன்படுத்தப்படும் போது மட்டுமே.

எடுத்துக்காட்டாக: எங்களிடம் 3 உள்ளீடு Ex-OR கேட் இருந்தால், ஒரு உள்ளீட்டிற்கு மட்டுமே “HIGH” என்ற தர்க்கத்தைப் பயன்படுத்தினால் (ஒற்றைப்படை தர்க்கம் “1”) வெளியீடு “HIGH” ஆக மாறும். இரண்டு உள்ளீடுகளுக்கு “HIGH” என்ற தர்க்கத்தை நாம் பயன்படுத்தினால் (இது “1” தர்க்கத்தின் எண்ணிக்கையும் கூட) வெளியீடு “LOW” ஆக மாறுகிறது.

3 உள்ளீட்டு பிரத்யேக அல்லது வாயில்:

3 உள்ளீட்டு EX-OR வாயிலின் விளக்கம்:

3 உள்ளீட்டு தர்க்கத்திற்கான உண்மை அட்டவணை EX-OR வாயில்:

| A (INPUT) | பி (INPUT) | சி (INPUT) | ஒய் (வெளியீடு) |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

3 உள்ளீட்டு Ex-OR வாயிலுக்கு பூலியன் சமன்பாடு பின்வருமாறு: A (BC) ̅ + A ̅BC ̅ + (AB) ̅C + ABC

நாம் முன்பு விவரித்தபடி, தர்க்கம் “Ex-OR” வாயில் ஒரு அடிப்படை தர்க்க வாயில் அல்ல, ஆனால் வெவ்வேறு தர்க்க வாயில்களின் கலவையாகும். தர்க்கம் “அல்லது” வாயில், தர்க்கம் “மற்றும்” வாயில் மற்றும் தர்க்கம் “NAND” வாயிலைப் பயன்படுத்தி Ex-OR வாயிலை பின்வருமாறு உணர முடியும்:

“பிரத்தியேக OR” வாயிலுக்கு சமமான சுற்று:

மேலே உள்ள வடிவமைப்பு பெரிய குறைபாட்டைக் கொண்டுள்ளது, ஒரு முன்னாள் அல்லது வாயிலை உருவாக்க எங்களுக்கு 3 வெவ்வேறு தர்க்க வாயில்கள் தேவை. ஆனால் லாஜிக் NAND வாயில்களுடன் மட்டுமே முன்னாள் OR வாயிலை செயல்படுத்துவதன் மூலம் இந்த சிக்கலை நாம் சமாளிக்க முடியும், இது புனையப்படுவதற்கும் சிக்கனமானது.

NAND வாயிலைப் பயன்படுத்தி பிரத்யேக அல்லது வாயில்:

எண்கணித செயல்பாடுகள், முழு சேர்ப்பவர்கள், அரை-சேர்ப்பவர்கள் போன்ற சிக்கலான கணினி பணிகளைச் செய்ய பிரத்யேக அல்லது வாயில்கள் பயன்படுத்தப்படுகின்றன, இது செயல்பாட்டைச் செயல்படுத்தவும் உதவும்.

லாஜிக் பிரத்தியேக அல்லது கேட் ஐசி 7486:

நீங்கள் சந்தையில் இருந்து லாஜிக் எக்ஸ்-ஓஆர் கேட்டை வாங்க விரும்பினால், மேலே உள்ள டிஐபி உள்ளமைவைப் பெறுவீர்கள்.

இது 14 ஊசிகளைக் கொண்டுள்ளது முள் # 7 மற்றும் முள் # 14 முறையே ஜிஎன்டி மற்றும் விசிசி. இது 5 வி இல் இயக்கப்படுகிறது.

பரப்புதல் தாமதம்:

பரப்புதல் தாமதம் என்பது வெளியீடு LOW இலிருந்து HIGH ஆகவும், உள்ளீட்டைக் கொடுத்த பிறகு நேர்மாறாகவும் மாறுவதற்கு எடுக்கப்பட்ட நேரம்.

LOW முதல் HIGH வரை பரப்புதல் தாமதம் 23 நானோ விநாடிகள்.

HIGH முதல் LOW வரை பரப்புதல் தாமதம் 17 நானோ விநாடிகள்.

பொதுவாக கிடைக்கக்கூடிய “EX-OR” கேட் ஐசிக்கள்:

- 74LS86 குவாட் 2-உள்ளீடு

- CD4030 குவாட் 2-உள்ளீடு

உங்களிடம் இன்னும் ஏதேனும் கேள்விகள் இருந்தால், மேலே உள்ள விரிவான விளக்கம் உங்களுக்கு என்ன தர்க்க வாயில்கள் மற்றும் தர்க்க வாயில்கள் எவ்வாறு செயல்படுகின்றன என்பதைப் புரிந்துகொள்ள உதவியிருக்கலாம் என்று நம்புகிறேன்? கருத்து பிரிவில் வெளிப்படுத்தவும், நீங்கள் விரைவான பதிலைப் பெறலாம்.

முந்தைய: மின்தேக்கி கசிவு சோதனையாளர் சுற்று - கசிவு மின்தேக்கிகளை விரைவாகக் கண்டறியவும் அடுத்து: டிஜிட்டல் இடையக - வேலை, வரையறை, உண்மை அட்டவணை, இரட்டை தலைகீழ், விசிறி-அவுட்